# NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

(Approved by AICTE, Affiliated to KTU University, Kerala)

### **ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT**

Course Material

S6:EC304: VLSI

About the Department:

Department of ECE established in 2002 with an intake of 60 students to undergraduate (B.Tech) programme and enhanced to an intake of 120 students from 2006. The department offers two Postgraduates(M.Tech) programmes in "Electronics". "Applied Electronics & Communication System" from 2011 with an intake of 18 students and "VLSI Design" from 2012 with an intake of 18. Highly qualified, experienced and dedicated staff members are the backbone of the Department. The Department always strive hard to satisfy the knowledge thirst of both students and faculties by organizing workshops / technical talks / conferences etc. The faculty members are actively involved in research work and regularly present/ publish their work in various national and international conferences / journals. The ECE Department is proud to host state-of- the art Laboratories in the area of VLSI, Embedded Systems, Microprocessor and Microcontrollers, Circuits, Analog and Digital Communication and Microwave and Optical communication. The ECE department formally inaugurated the ECHOS (The ECE Association) in 2009 and under this banner many extra-academic activities have been conducted such as paper presentation, quiz competition, workshops and seminars. Also the department has two magazines that have been developed on the basis of the creative skills of our imaginative students. There is an Embedded Club that meets on monthly basis to discuss innovative projects and publication based activities. Department is closely associated with INSTITUTE OF ELECTRONICS & TELECOMMUNICATION ENGINEERS (IETE) Palakkad Centre to organize technical events like guest lecture, seminars and conferences.

#### Vision of the institute:

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

#### Mission of the institute:

NCERC is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values. We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

### Vision of the department:

Providing Universal Communicative Electronics Engineers with corporate and social relevance towards sustainable developments through quality education.

#### Mission of the department:

- 1) Imparting Quality education by providing excellent teaching, learning environment.

- 2) Transforming and adopting students in this knowledgeable era, where the electronic gadgets (things) are getting obsolete in short span.

- 3) To initiate multi-disciplinary activities to students at earliest and apply in their respective fields of interest later.

- 4) Promoting leading edge Research & Development through collaboration with academia & industry.

#### **Program Educational Objectives (PEOs)**

- I. To prepare students to excel in postgraduate programmes or to succeed in industry / technical profession through global, rigorous education and prepare the students to practice and innovate recent fields in the specified program/ industry environment.

- II. To provide students with a solid foundation in mathematical, Scientific and engineering fundamentals required to solve engineering problems and to have strong practical knowledge required to design and test the system.

- III. To train students with good scientific and engineering breadth so as to comprehend, analyze, design, and create novel products and solutions for the real life problems.

- IV. To provide student with an academic environment aware of excellence, effective communication skills, leadership, multidisciplinary approach, written ethical codes and the life-long learning needed for a successful professional career.

#### **Program Outcomes (Pos):**

- 1. **Engineering Knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem Analysis**: Identify, formulate, research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of Solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct Investigations of Complex Problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern Tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The Engineer and Society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal, and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and Sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and Team Work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project Management and Finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. **Life-long Learning:** Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

#### Program Specific Outcomes (PSO):

- 1. Facility to apply the concepts of Electronics, Communications, Signal processing, VLSI, Control systems etc., in the design and implementation of engineering systems.

- 2. Facility to solve complex Electronics and communication Engineering problems, using latest hardware and software tools, either independently or in team.

# Mapping of PEOs with the Program Outcomes (POs):

The Electronics and Communication Engineering Program outcomes leading to the achievement of the objectives can be summarized in the following Table.

|      |   |   | Program Outcomes |   |   |   |   |   |   |   |   |   |

|------|---|---|------------------|---|---|---|---|---|---|---|---|---|

|      |   | а | b                | С | d | e | f | g | h | i | j | k |

|      | 1 | X | X                | X |   |   |   |   |   |   |   | X |

| PEOs | 2 | X | X                | X | X |   | X |   |   |   |   | X |

| PEUS | 3 |   | X                | X | X | X |   |   |   |   | X |   |

|      | 4 |   |                  |   | X | X | X | X | X | X | X | X |

#### **Course Outcome:**

After completion of this course the students will be able to

- 01. Understand and describe material preparation, diffusion, oxidation and ion implantation.

- 02. Knowing the epitaxial and lithography process in the IC Fabrication with the isolation methods.

- 03. Describe, analyze, formulate and construct CMOS Inverters with layout design rules

- 04. Understand and explain MOSFET logic design in the bank end process

- 05. Demonstrate basics of Different Type of Memory and Sensing Circuits.

- 06. Demonstrate the function of Adders and Multiplier techniques

# **CO-PO Mapping**

| CO/PO | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| CO1   | 3   | 2   | 1   |     |     |     |     |     |     | 1    | 2    |      |

| CO2   |     | 3   |     |     | 2   |     |     |     |     | 1    | 2    |      |

| CO3   |     | 3   | 2   |     | 1   |     |     |     |     | 1    | 2    |      |

| CO4   | 2   | 3   |     |     |     |     |     |     |     | 1    | 2    |      |

| CO5   |     | 3   |     |     | 2   |     |     |     |     | 1    | 2    |      |

| CO6   |     | 2   | 2   |     | 3   |     |     |     |     | 1    | 2    |      |

#### **COURSE PLAN:**

- 1 Introduction to VLSI

- 2 Material Preparation Production of EGS

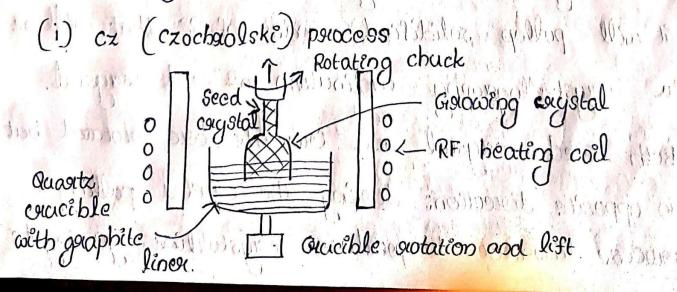

- 3 Crystal Growth CZ Process and FZ Process

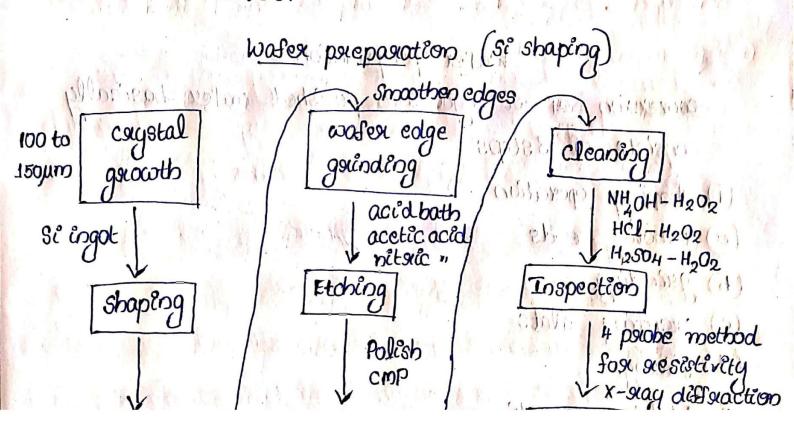

- 4 Wafer Preparation

- 5 Thermal Oxidation Growth Mechanism

- 6 Dry Wet Oxidation Deal & Grove Model

- 7 Diffusion Ficks laws Diffusion with constant surface

- 8 Ion Implantation Range Theory Annealing

- 9 Epitaxy VPE & MBE

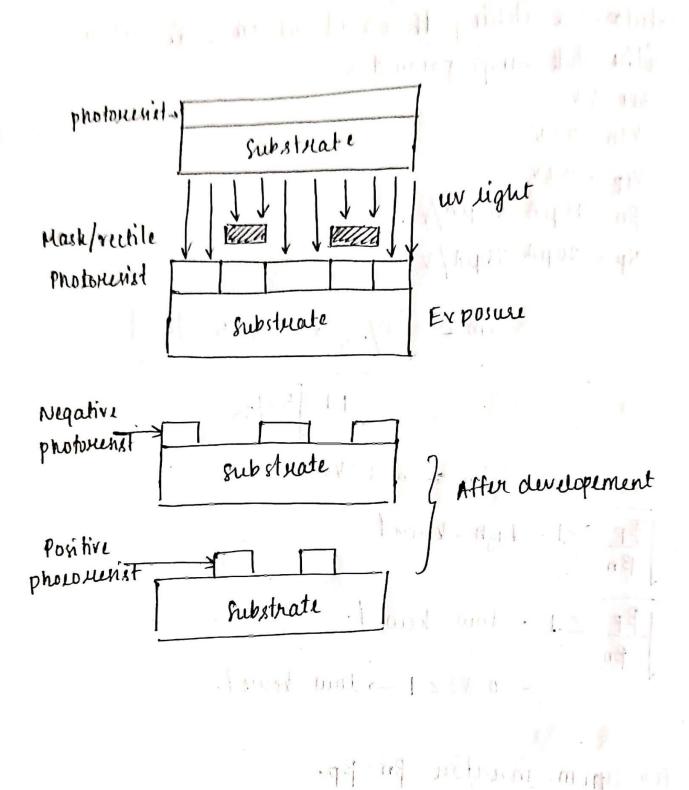

- 10 Lithography Photo lithography Steps

- 11 Electron beam lithography Etching & Metal deposition

- 12 Component fabrication Transistor

- 13 Fabrication Diode Resistor Capacitor

- 14 N Well CMOS IC fabrication

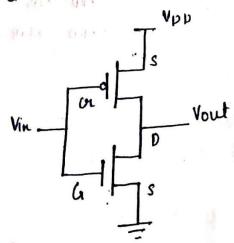

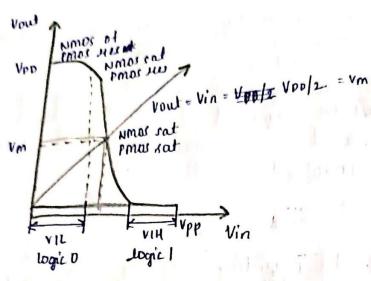

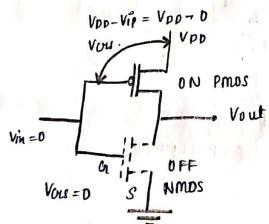

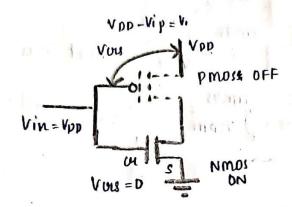

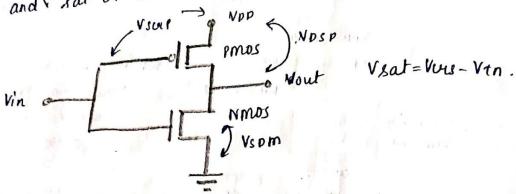

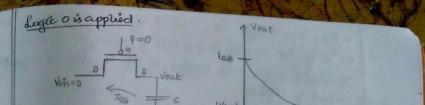

- 15 CMOS Invertors DC Characteristics

- 16 Switching Chara of CMOS Invertor

- 17 Power dissipation of CMOS Invertor

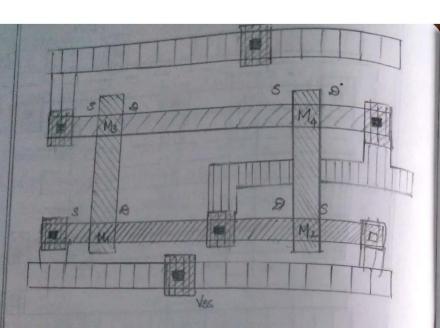

- 18 Layout Design rules Stick diagram

- 19 Layout of CMOS Invertor

- 20 Layout of 2 input NAND & NOR gates

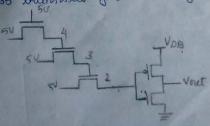

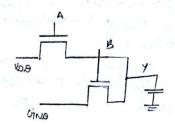

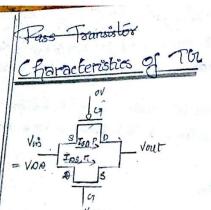

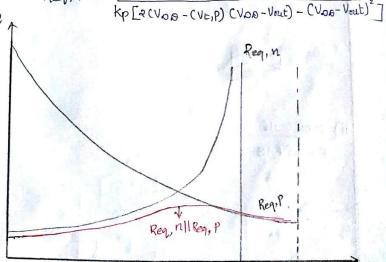

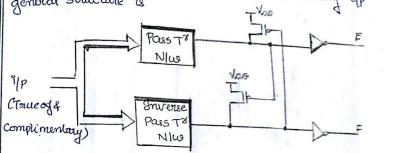

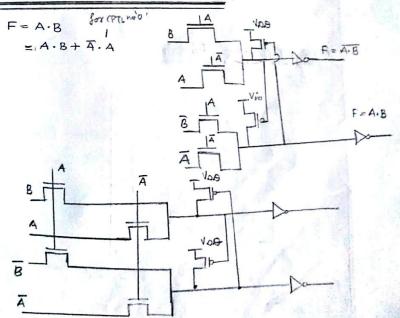

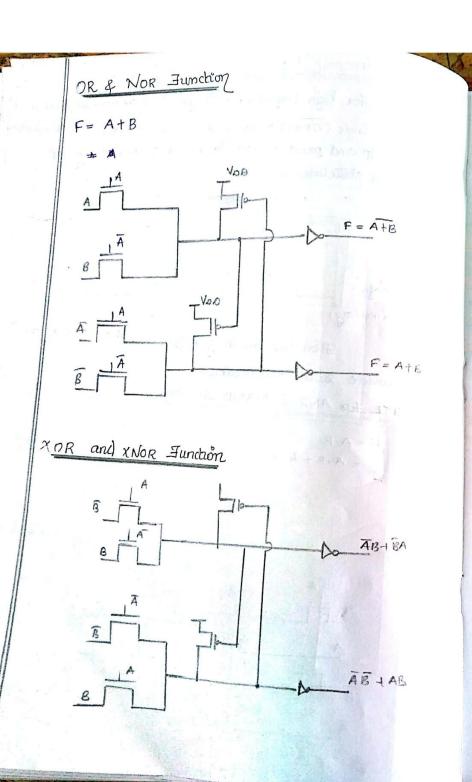

- 21 Pass transistor Logic

- 22 Complementary Pass Transistor Logic

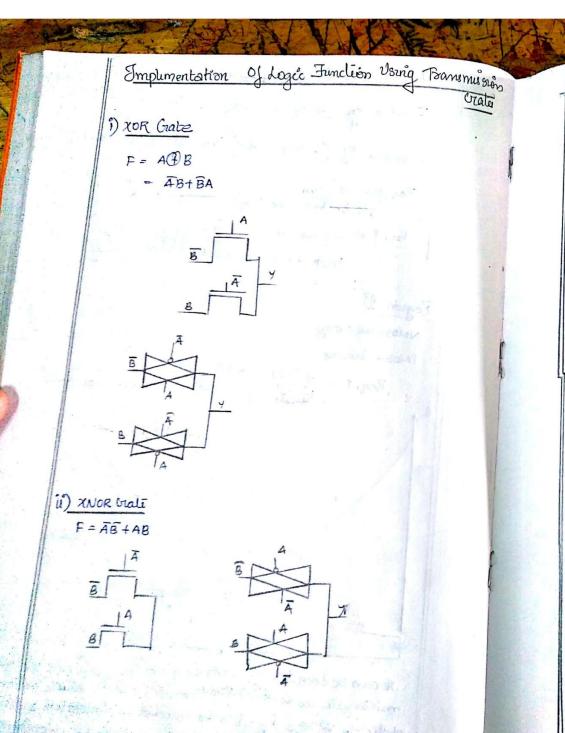

- 23 Transmission gate logic

- 24 Realization of functions

- 25 Realization of functions

- 26 4 x 4 MOS ROM Cell array(OR NOR NAND)

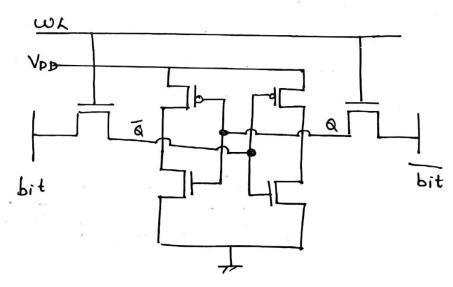

- 27 SRAM Six transistor

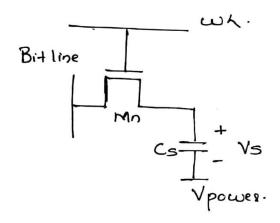

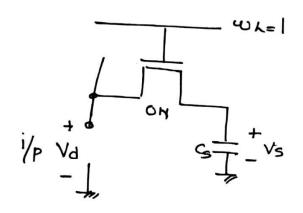

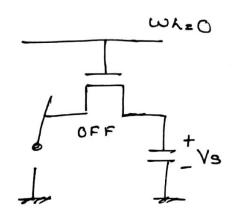

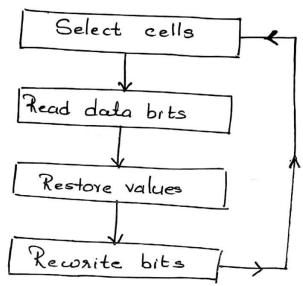

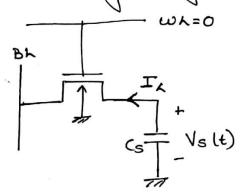

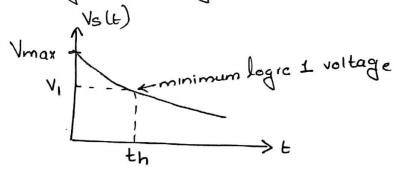

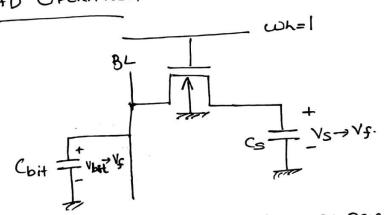

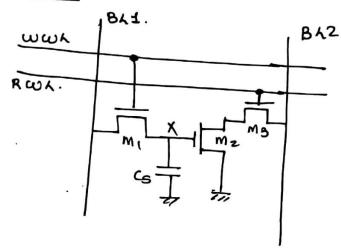

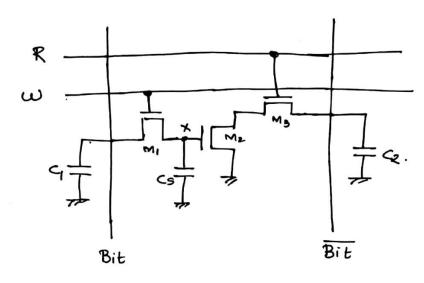

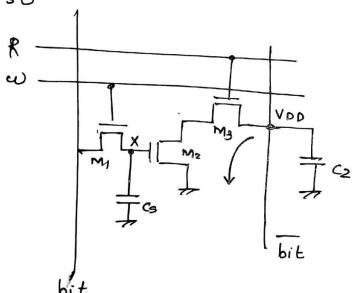

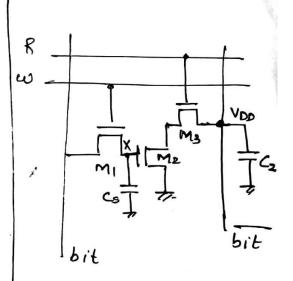

- 28 DRAM Three transistor & One Transistor Dynamic Memory Cell

- 29 Sense Amplifiers Inroduction

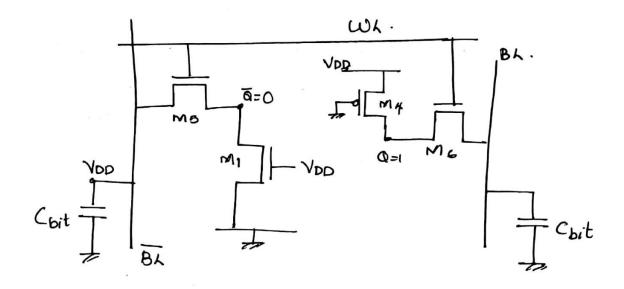

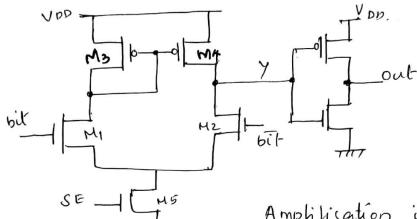

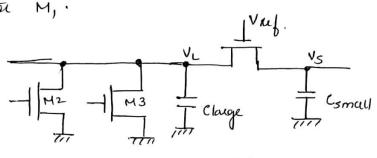

- 30 Differential Voltage Sensing Amplifiers

- 31 Introduction to PLDs & FPGAs

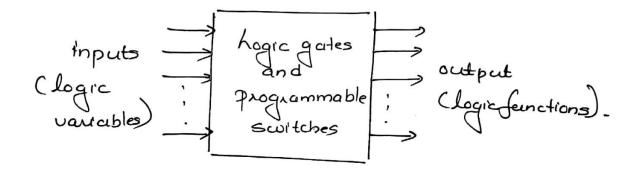

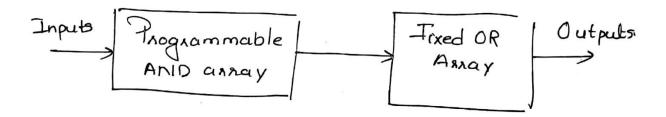

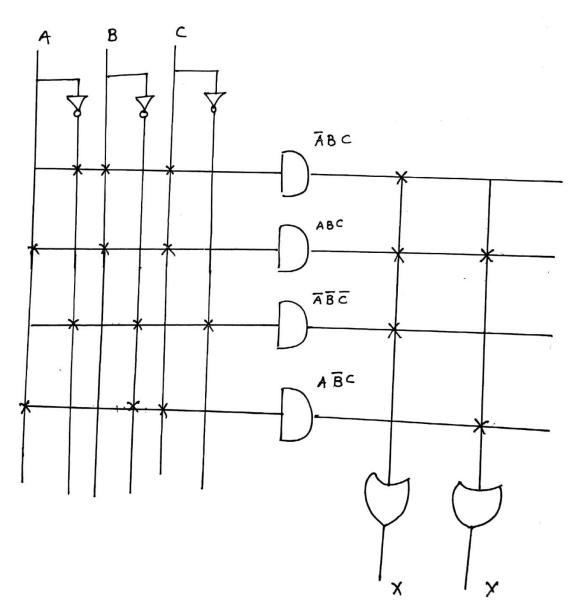

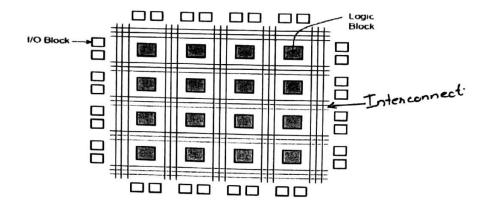

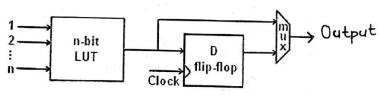

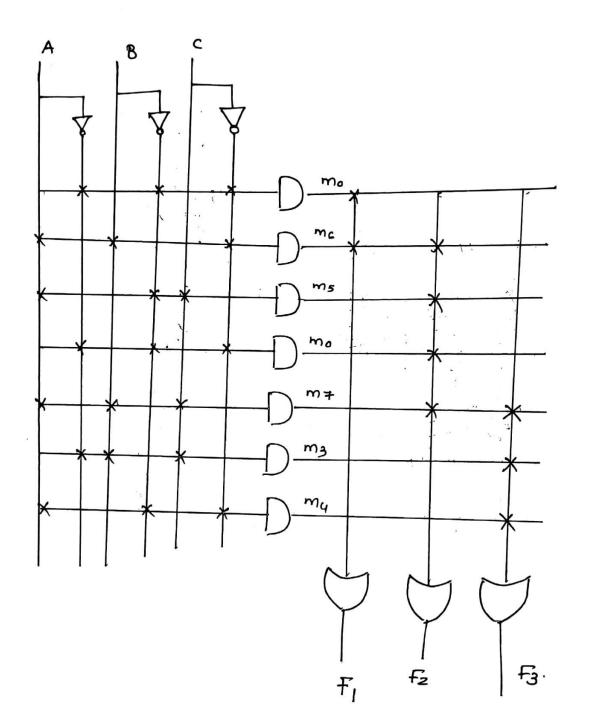

- 32 Design of PLAs

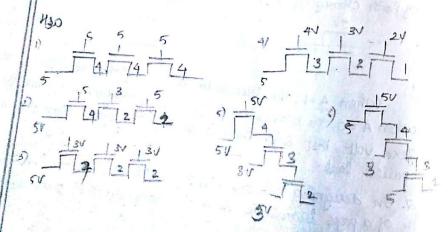

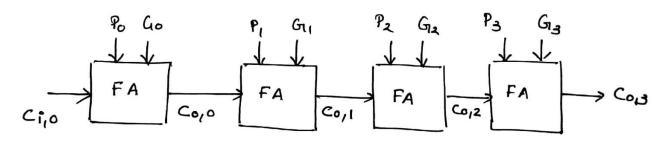

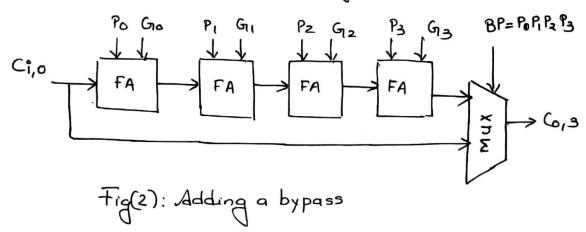

- 33 Adders Static adder Carry By pass adder

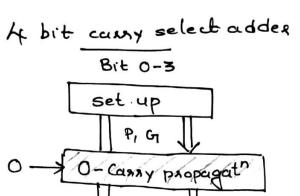

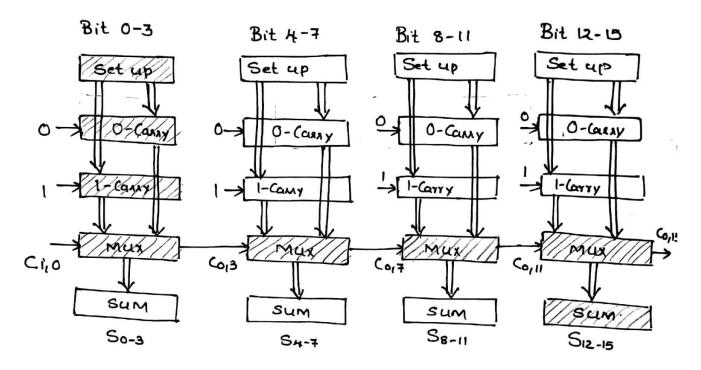

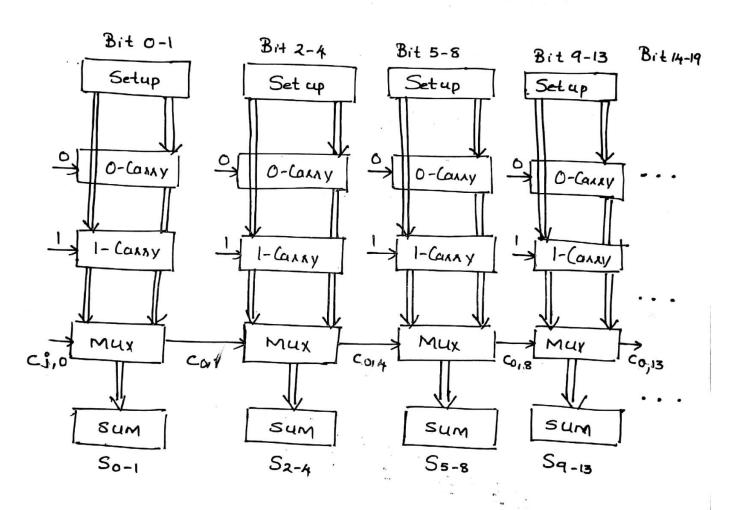

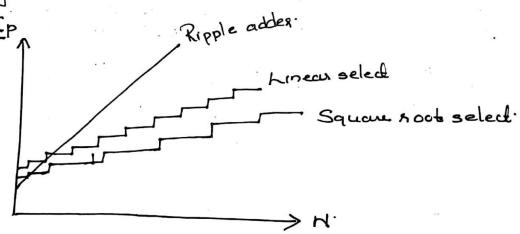

- 34 Linear carry select adder

- 35 Square root carry select adder

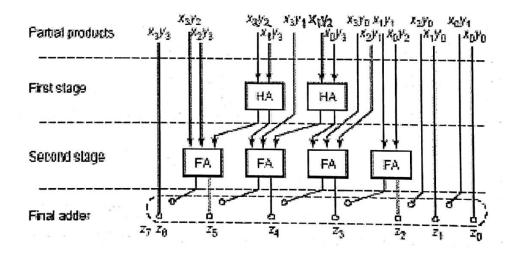

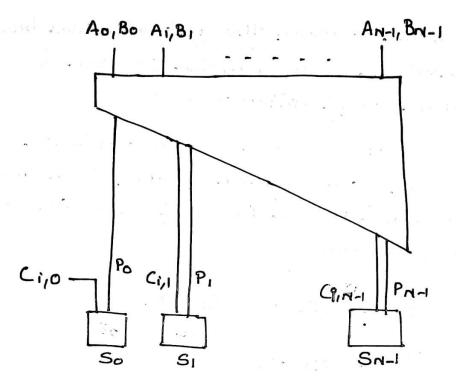

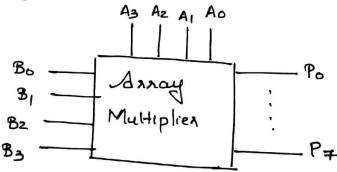

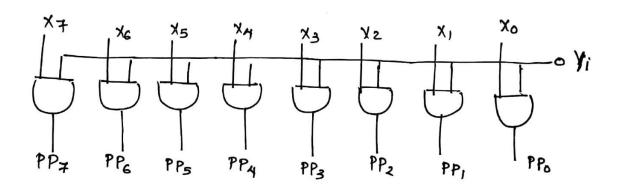

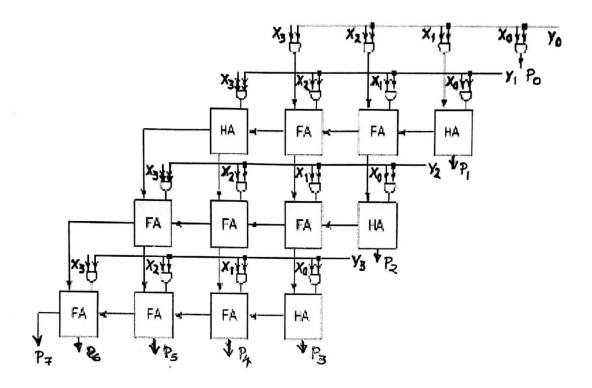

- 36 Multiplier Array multiplier

| COURSE |             |         | YEAR OF      |

|--------|-------------|---------|--------------|

| CODE   | COURSE NAME | L-T-P-C | INTRODUCTION |

| EC304  | VLSI        | 3-0-0-3 | 2016         |

Prerequisite: EC203 Solid State Devices, EC204 Analog Integrated Circuit.

#### **Course objectives:**

- To give the knowledge about IC Fabrication Techniques

- To impart the skill of analysis and design of MOSFET and CMOS logic circuits.

#### **Syllabus:**

IC Fabrication Technology, CMOS IC Fabrication Sequence, CMOS inverters, Design rules, Static CMOS Design, Dynamic CMOS circuits, Pass transistor, Read Only Memory, Random Access Memory, Sense amplifiers, Adders, multipliers, Testing of VLSI circuits.

#### **Expected outcome:**

The students will be able to design and analyse various MOSFET and CMOS logic circuits.

#### Text Books:

- 1. John P Uyemura, Introduction to VLSI Circuits and Systems, Wiley India, 2006

- 2. S.M. SZE, VLSI Technology, 2/e, Indian Edition, McGraw-Hill,2003

#### **References:**

- 1. Jan M.Rabaey, Digital Integrated Circuits- A Design Perspective, Prentice Hall, Second Edition, 2005.

- 2. Neil H.E. Weste, Kamran Eshraghian, Principles of CMOS VLSI Design- A Systems Perspective, Second Edition. Pearson Publication, 2005

- 3. Razavi Design of Analog CMOS Integrated Circuits,1e, McGraw Hill Education India Education, New Delhi, 2003.

- 4. Sung –Mo Kang & Yusuf Leblebici, CMOS Digital Integrated Circuits- Analysis & Design, McGraw-Hill, Third Ed., 2003.

- 5. Yuan Taur & Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 2008

| Course Plan |                                                                                                                                                                                             |       |                              |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|--|--|--|--|

| Module      | Course content                                                                                                                                                                              | Hours | End<br>Sem.<br>Exam<br>Marks |  |  |  |  |

| Ţ           | Material Preparation- Purification, Crystal growth (CZ and FZ process), wafer preparation Thermal Oxidation- Growth mechanisms, Dry and Wet oxidation, Deal Grove model.                    | 4     | 15                           |  |  |  |  |

| I           | <b>Diffusion-</b> Fick's Laws, Diffusion with constant surface concentration and from a constant source, diffusion techniques. <b>Ion implantation</b> -Technique, Range Theory, annealing. | 3     |                              |  |  |  |  |

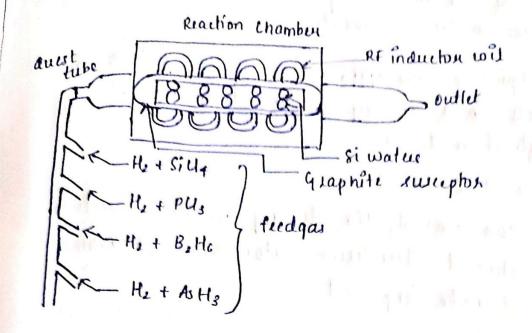

| Ш           | <b>Epitaxy :</b> Vapour phase epitaxy and molecular beam epitaxy <b>Lithography-</b> Photo lithographic sequence, Electron Beam  Lithography, Etching and metal deposition                  | 4     | 15                           |  |  |  |  |

| 11          | Methods of isolation Circuit component fabrication: transistor, diodes, resistors, capacitors, N-well CMOS IC Fabrication Sequence                                                          | 3     | 15                           |  |  |  |  |

|             | FIRST INTERNAL EXAM                                                                                                                                                                         |       |                              |  |  |  |  |

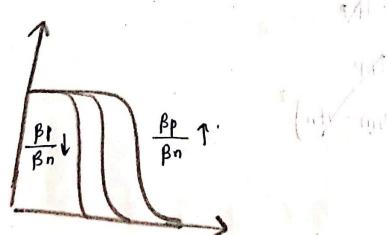

| III         | <b>CMOS inverters</b> - DC characteristics, switching characteristics, power dissipation                                                                                                    | 4     | 15                           |  |  |  |  |

|    | <b>Layout Design rules</b> , Stick Diagram and layout of CMOS Inverter, two input NAND and NOR gates                                                                          | 4 |    |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|--|--|--|--|

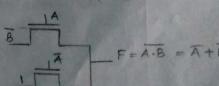

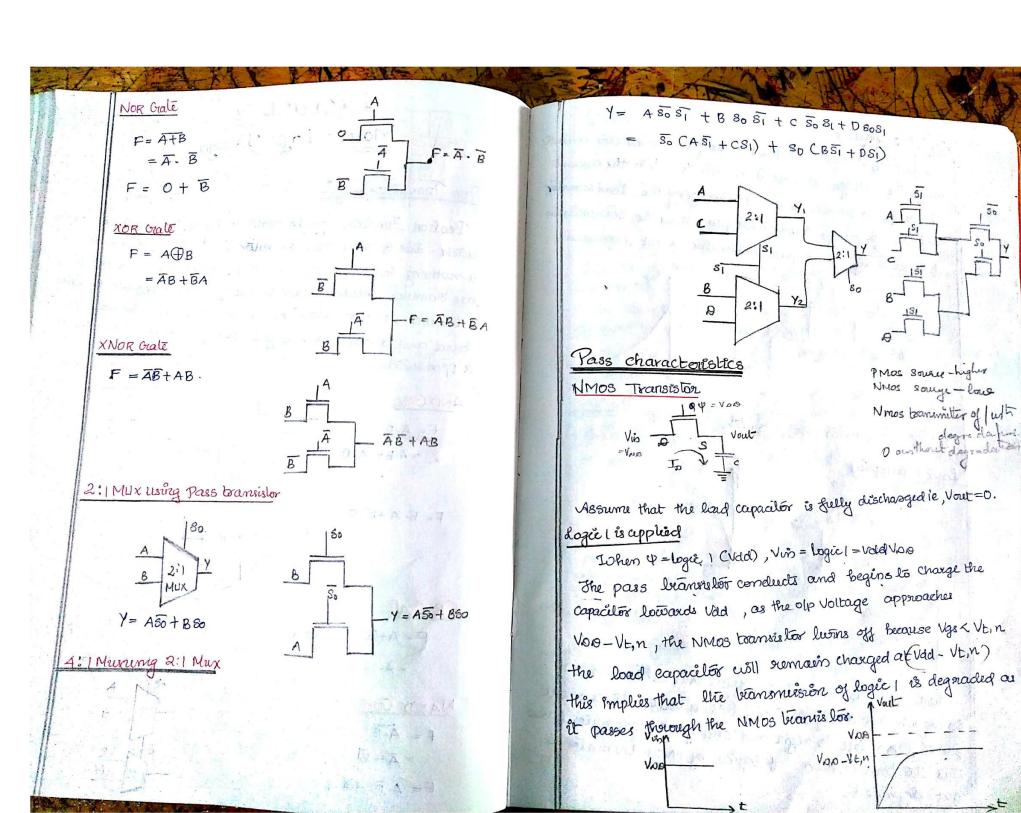

| IV | MOSFET Logic Design -Pass transistor logic,<br>Complementary pass transistor logic and transmission gate<br>logic, realization of functions                                   | 6 | 15 |  |  |  |  |

|    | SECOND INTERNAL EXAM                                                                                                                                                          |   |    |  |  |  |  |

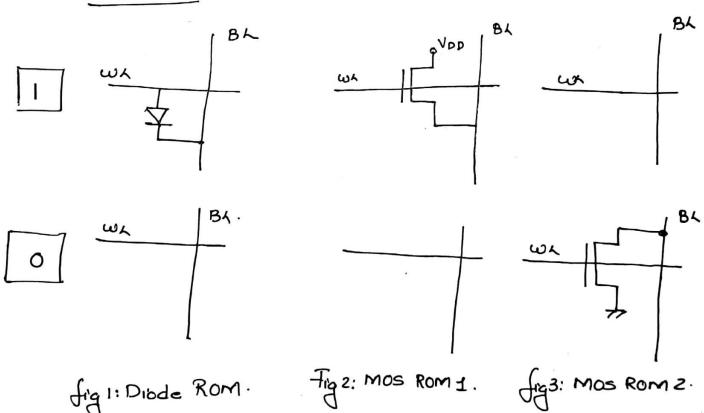

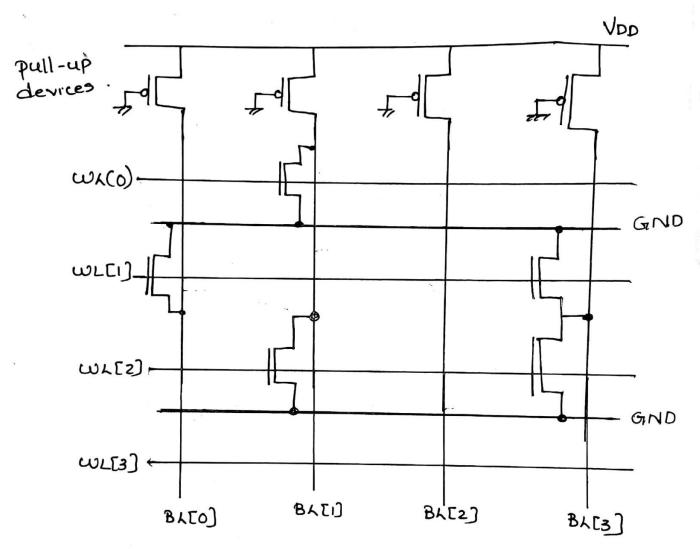

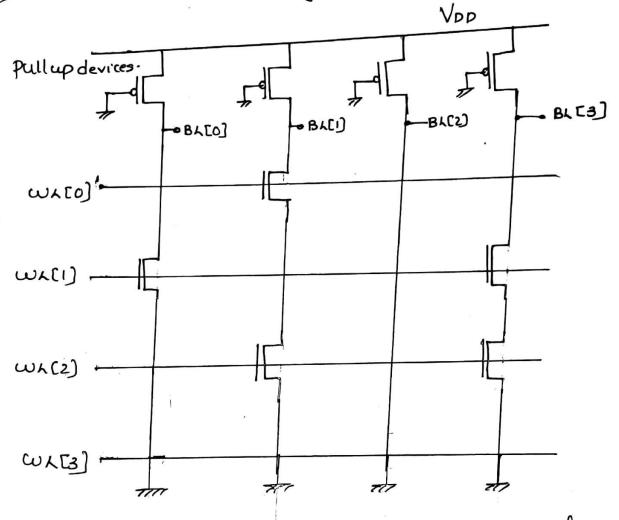

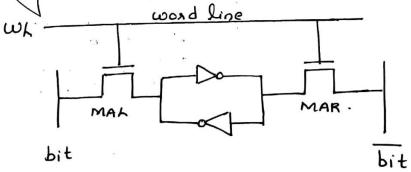

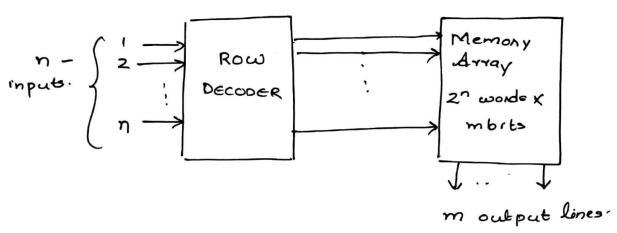

| V  | Read Only Memory-4x4 MOS ROM Cell Arrays(OR,NOR,NAND) Random Access Memory –SRAM-Six transistor CMOS SRAM cell, DRAM –Three transistor and One transistor Dynamic Memory Cell | 4 | 20 |  |  |  |  |

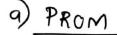

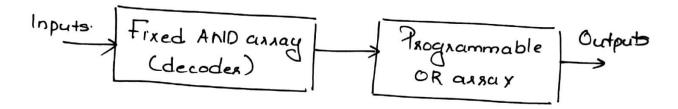

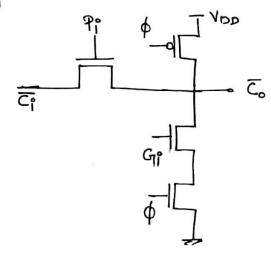

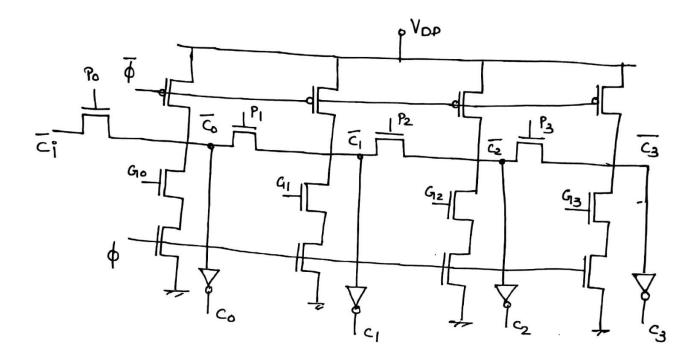

|    | Sense amplifiers –Differential Voltage Sensing Amplifiers Introduction to PLDs and FPGAs, Design of PLAs.                                                                     | 3 |    |  |  |  |  |

| VI | Adders- Static adder, Carry-By pass adder, Linear Carry-Select adder, Square- root carry- select adder Multipliers-Array multiplier                                           | 4 | 20 |  |  |  |  |

|    | END SEMESTER EXAM                                                                                                                                                             |   |    |  |  |  |  |

## **Question Paper Pattern (End Semester Exam)**

Maximum Marks: 100 Time: 3 hours

The question paper shall consist of three parts. Part A covers modules I and II, Part B covers modules III and IV, and Part C covers modules V and VI. Each part has three questions uniformly covering the two modules and each question can have maximum four subdivisions. In each part, any two questions are to be answered. Mark patterns are as per the syllabus with 70% for theory and 30% for logical/numerical problems, derivation and proof.

- I. What is the need of SiOi layer in MOS fabrication process?

- 2. State the laws governing the diffusion process.

- 3. Compare wet and dry oxidation.

- 4. Write down the range equation for ion implantation and explain each term in it.

- s. What are oxides related capacitance and junction capacitance?

- 6. Explain float zone process of crystal growth. What are its advantages and disadvantages over Czochralski growth?

- 7. What are the different processes involved in silicon wafer preparation?

- 8. Explain Czochralski technique of crystal growth.

- 9. Explain the slicing and polishing of silicon wafers and the purpose of notch on the wafer.

- 10. Explain the essential steps in IC fabrication.

- i 1. Derive the Deal-Grove model of oxidation.

- 12. With neat sketch, explain ion implantation process.

- 13. Draw the limited source and constant source diffusion profiles and distinguish them in terms of relevant modelling equations.

- 14. Explain the oxidation growth mechanism with a neat diagram.

- 15. Explain the CZ and FZ process for crystal growth and compare them.

- 16. What is oxidation induced stacking fault and how it can be eliminated?

- 17. Write the difference between pre-deposition and drive-in processes.

- 18. What are the different diffusion mechanisms, explain?

- 19. Explain the different types of ion stopping mechanisms.

- 20. What is called annealing and how it differs from rapid thermal annealing.

- 21. Write the equation of projected range and define each term in it.

- 1. Mention the types of resistor fabricated in IC environment.

- 2. What is lithography?

- 3. With the help of neat diagrams, explain the steps involved in i) Photolithography ii) X-ray lithography.

- 4. List the n well IC fabrication sequence.

- S. Comment briefly on the characteristics of an exposure tool used for lithographic process.

- 6. What are the properties of metals used for metallization?

- 7. What are the undesirable capacitances formed in MOS fabrication?

- 8. Assuming Gaussian distribution for the ion implantation, find the distance from the surface at which the ion concentration falls to half the peak value, for arrange of 0.1q. The straggle value is 0.02s.

- 9. Explain how resistors and capacitors are fabricated on an IC chip.

- 10. What are positive and negative photoreists, explain.

- i1. What are the important criterions for hetero epitaxy of material A to be possible on a single crystal substrate of material B?

- 12. What is boundary layer problem? How can it be minimised in a horizontal epitaxy system?

- 13. Explain any one method of epitaxial growth, with diagram.

- 14. With diagrams, explain the steps involved in the fabrication of a n-well CMOS IC.

- 15. What is electron beam lithography?

- 16. Explain the different types of etching techniques.

- 17. Explain CVD system for epitaxial growth.

- i8. Explain the molecular beam epitaxy, with neat diagrams.

- 19. Explain the different types of metal deposition techniques.

- 20. What is the difference between diffusion and epitaxy7

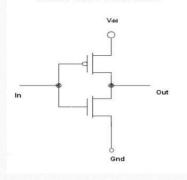

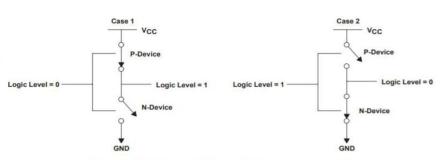

- 1. Compare the features of CMOS and bipolar technologies.

- 2. Define threshold voltage for a MOS transistor. What are the parameters on which it depends on?

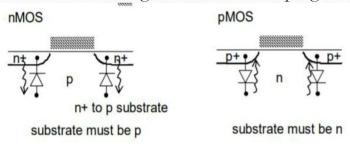

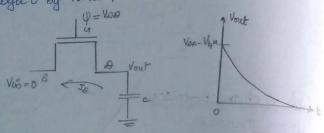

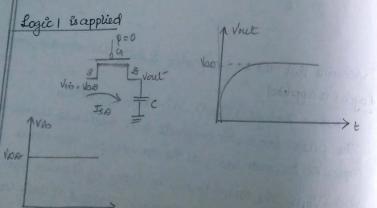

- 3. PMOS is perfect switches for transmission of logic 1 while NMOS is perfects for transmission of logic 0. Justify the statement.

- 4. Draw the structure of CMOS p-well inverter.

- 5. Why NMOS technology is preferred more than PMOS technology?

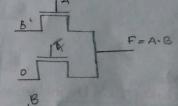

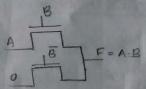

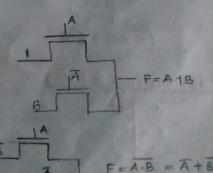

- 6. **Draw** the Stick diagram, circuit diagram, of i)NMOS inverter ii)CMOS inverter

- 7. Realize the equation Y=(AB+CD)' in i)NMOS technology ii)CMOS technology

- 8. Draw the stick diagram of the function, F=(AB+E+CD)'

- 9. Define the noise margin for CMOS inverter.

- 10. Derive expression for switching threshold of a CMOS inverter.

- 11. Derive graphically, the CMOS inverter characteristics.

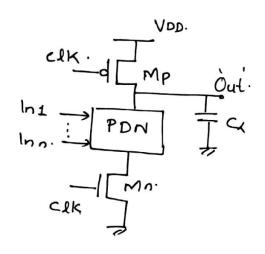

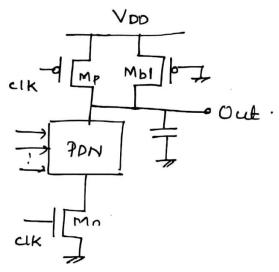

- 12. What is meant by charge leakage in dynamic CMOS logic? Explain a method to prevent it.

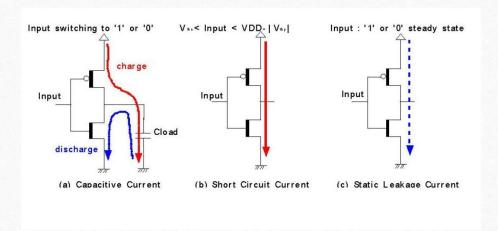

- 13. Explain static power dissipation and short circuit power dissipation with reference to CMOS logic.

- 14. What are the different regions of operation of MOS transistor? How are they related to Vgs, Vds and Vt for nmos and pmostransistors?

- **15.** Calculate the dynamic power dissipation in achip operating with Vdd of SV at 100MHz with an internal switched capacitance of 300pF.

- 16. Explain the CMOS inverter DC characteristics with the region of operation in detail.

- 17. Draw the circuit diagram and stick diagram for implementing the logic function F=A. (B+C)' in static p well CMOS logic.

- 18. Draw the stick diagram and layout of 2 input NAND gate.

- 19. Draw the stick diagram and layout of 2 inputs NOR gate.

- 20. Derive the expression for dynamic power dissipation in a static CMOS inverter.

- 21. For a CMOS circuit CL =15fF/gate, ADD =2•5V Rd tp'35ps.If there are lo' gates/chip, determine the dynamic power dissipation at the maximum frequency of operation.

- 1. What is meant by charge leakage in dynamic logic? How it is prevented?

- 2. DraW the layout of a 4 input AND/NAND gate in complementary pass transistor logic.

- 3. Draw the circuit schematic of 2 input multiplexer using transmission gates.

- 4. What is np-domino logic?

- 5. How is charge leakage and sharing problems rectified in dynamic logic?

- 6. Write down the basic principle of dynamic CMOS logic with circuit diagram.

- 7. Draw the circuit diagram of transmission gate XOR logic and explain its operation.

- 8. Draw the circuit of a 4 input NOR gate in domino logic. What are the advantages of domino logic?

- 9. Design pass transistor logic for 2 input XNOR gate.

- 10. Implement a 2x1 mux using transmission gates.

- 11. Implement a 4x1 mux using transmission gates.

- 12. Draw a 2 input XNOR using transmission gates.

- 13. Explain the operation of NMOS and PMOS transistor operation in transmission gates.

- 14. Explain the function of complementary pass transistor.

- i5. Draw 2 input NAND gate in static CMOS.

- 16. Implement the function F—AB(C+D)+DE using static CMOS technology.

- 17. Compare pass transistor logic and complementary pass transistor logic.

- 18. Draw a 2 input XOR using transmission gates.

- 19. What are the advantages and disadvantages of domino logic?

- 20. Design a multiplexer using CMOs pass transistor logic and explain its operation with its truth table.

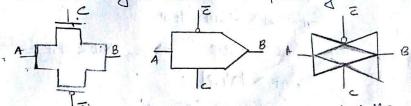

- 21. Give the different symbols for transmission gates.

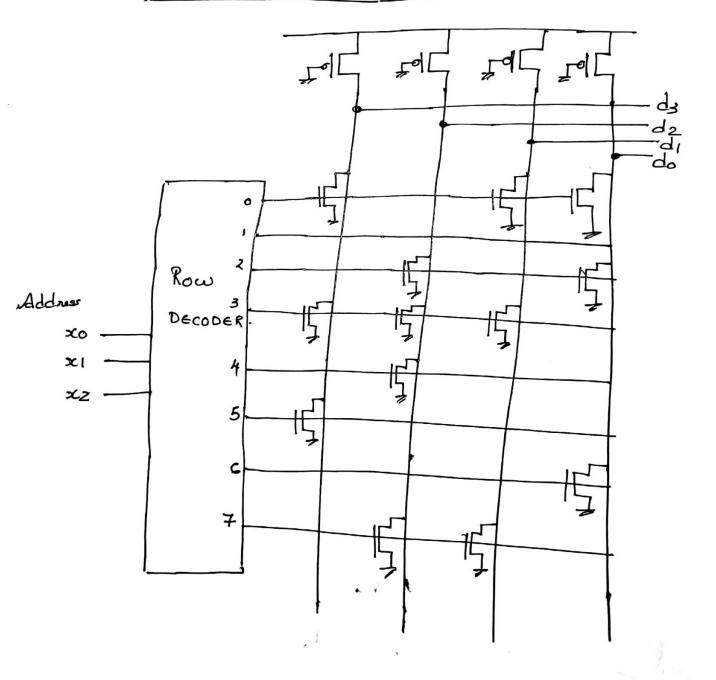

- i. With the help of a circuit diagram give proper explanation for the **confi guration of 4x4** NOR-Rom array.

- 2. Write short note on FPGA.

- 3. Draw the circuit diagram of s sense amplifier and give explanation on how the sensing of operation is carried out in SRAM cell.

- 4. Draw a 6T SRAM cell.

- 3. What is the function of CLB in FPGA?

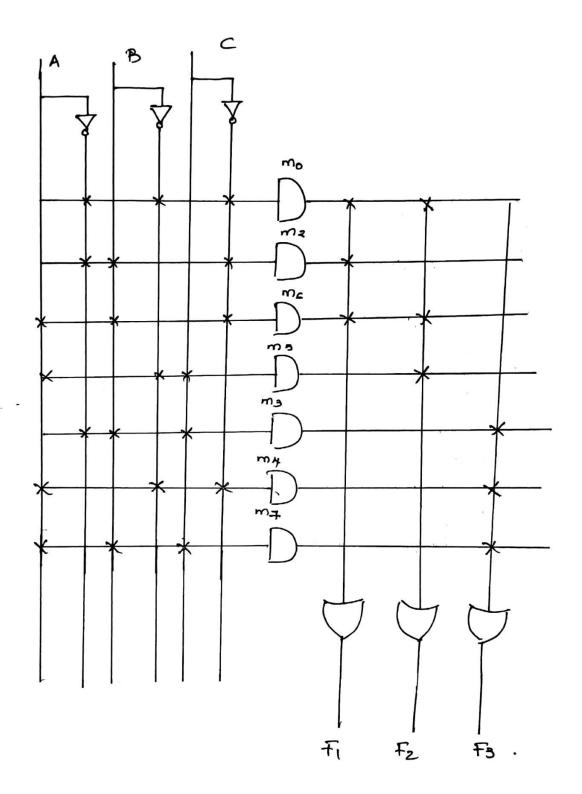

- 6. Design an AND-OR PLA with putputs,Fl=m0+m2+m6, P2=m0+m5+m6, F3=m3+m4+m7.

- 7. Draw and explain the schematic and physical structure of a DRAM cell using a trench capacitor

- 8. Design an FET programmable ROM with the following data.

| Address | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|---------|------|------|------|------|------|------|------|------|

| Data    | 0100 | 1111 | 1010 | 0001 | 1011 | 0111 | 1110 | 1001 |

- 9. What are the functions of sense amplifier?

- 10. Draw the circuit diagram of a 3 transistor dynamic RAM cell and explain its operation.

- 11. Show the CMOS implementation of a OR-ROM cell to store 8 words of 8 bits.

- 12. With cross sectional view, explain the principle of an EPROM cell.

- 13. Show the CMOS implementation of a NOR ROM cell to store 4 words of 4 bits which are as follows 1011,0110,1001 and 1100.

- 14. Draw a Master slave MUX based latch pair using transmission gates and inverters and explain its operation.

- 15. Design a PLA for realizing the following outputs.

- f 1'Z ,2,6,7, f 2 = Z3,5,7,9, f 3=1,3,8,12

- 16. Draw and explain multiplexer based positive edge- triggered register using master slave configuration.

- 17. What are the advantage and disadvantages of dynamic latches and registers over static implementations?

- 18. Compare dynamic RAM and static RAM.

- 19. Using a suitable PLA, design and implement a 4 bit binary to gray code.

- 20. What is the purpose of sense amplifier? Describe the working of a single ended sense amplifier.

- 21. Draw a DRAM memory cell.

- 22. Draw a ROM array to store a set of eight 8 bit data using MOS based ROM. Explain how they are written and read.

- 23. Design an AND-OR PLA with outputs Fl=ml+m6, F2=m0+m5+m6+in7 F3=m3+m4+m7

- 1. Implement a linear 16 blt carry select adder using 4 bit carry Select adder blocks. How does a square root carry select improve the performance?

- 2. Discuss the principle of Wallace Tree Multiplier. How is the propagation delay reduced as compared to simple array multiplier?

- 3. Design a 14 bit square root carry select adder. Calculate the worst case delay.

- 4. Show the design of a 32 bit carry select adder based on 4 bit or similar ripple carry adder. Find the total gate delay for your design.

- 5. Explain the operation of carry bypass adder.

- 6. Draw the logic circuit for a 4 bit carry look ahead adder.

- 7. De5ign a 4x4 array multiplier.

- 8. Design an 8 bit carry select adder.

- 9. With the help of suitable diagrams, explain how delay computation time is reduced in carry look ahead adder.

- 10. Explain the partial product accumulation in a Wallace tree multiplier.

- 11. Explain the operation of NxM bit array multiplier.

- 12. Show the critical path in a linear carry select adder scheme and give the expression for critical path delay involved.

- 13. Explain the principle of a register based multiplier.

- 14. How is booth encoding used to speed up multiplication process?

- 15. How are carry look ahead adder module interconnected to get higher order adders?

- 16. Explain the working of carry bypass adder.

- 17. Explain square root carry select adder and derive the expression for time delay and **compare** its performance with other adders.

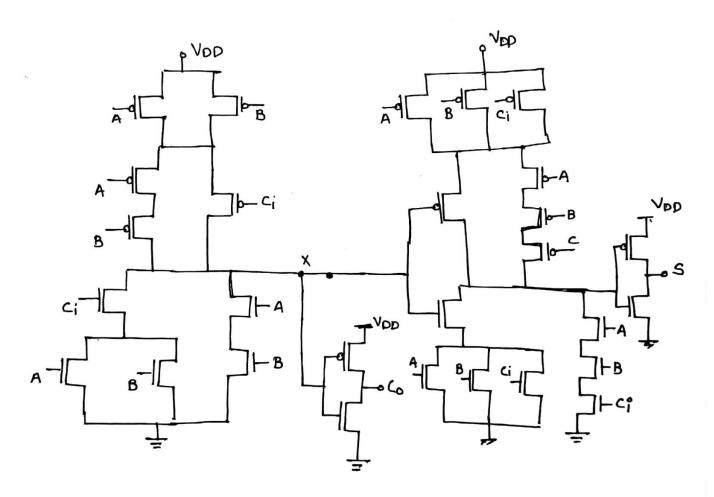

- 18. With diagram explain the implementation of 4 bit carry look ahead generatorin dynam» CMOS logic.

- 19. Compare the performance of linear carry select adder and square root carry select adds.

- 20. Explain the working of static adders.

- a) why silicon is used over Germanium in chip?

- D) It is cheaped and sion is more stable than Geor.

High interestic impedance.

$$5iO_2 + c$$

Hightemp.  $\Rightarrow 8ic$

It has high imposity (nois)

. It is convented into Electronic grade Silicon (EGS)

B

$$35 - 50 \stackrel{\checkmark}{=} 0.01$$

C9  $50 - 200 \stackrel{\checkmark}{=} 0.01$

CU  $15 - 60 \stackrel{\checkmark}{=} 0.1$

N°  $20 - 100 \stackrel{0.1}{=} 0.5$

D  $20 - 50 \stackrel{\checkmark}{=} 0.5$

- (i) material pereparation

- (ii) St. oxidation man by the sounds to me

- (iii) Imparity Diffusion (iii)

- (iv) Ion implantation

- (v) Lithography

- (vi) Etching

- (vii) Thin silm deposition

- (viii) Epitaxial gasouth

- (a) metalisation

- (i) material personation

It involves 3 steps they one:

- · purification Natural sand into Eas

- · caystal gaowth caeation of ignots using Cz oa Fz padcess.

0001 01 OCA - 1130

· Waser pereparation - Ignot into water

# Pulsication

Si occuring naturally in the fourm of silica and silicates is the most impositant semiconductor for electronic simpositant composed to Ge, se excels for inflowing seasons,

> Si clevices can operate at high temperature.

> Internace nesistivity is higher.

-> SiO2 is mode stable than GeO2.

> It is also water soluble.

> si is available in los cost

Goal of material preparation & preparing righ impurity st caystal worker. St worker refers to a single caystal of st with a specific orientation siesistivity and dopant concentration. Starting muierial of si ausea manufacture is electronic grade silicon. EGS perepased suom MGB (metalluggical Guade silicon mas is synthesized from the one (sond on auatrite). The one is neduced to si by micing with excess of coxbon (coal, chowood chips) and heating in submerged electrode ouc funace. The 9:02 seact with excess carbon to seast form selicon combide (sec) at high temperature sic react with side to form si. Secre + Seo, (s) -> Si(Q) + Seo(9) + Co(9)

This is mas and it is 90% pa To convert MGis to EGS 1) Pysiolysis Method Sitty + Heat -> 82 + 2H2 si 44 (silone) EGS can be paroduced by pyerolysis method in which silone (sity) will be acacted with beat. The acucaron takes place at high temperature of 900c. The main advantage of using silane instead of Tolichlogo silane is lower production cost and less padaction of hadmfal bypacoduct

2) Siemann's process

Sithy + Heat Heat

Sithy + Heat

Sit

deposition

258Hcl3 + 2H2 -> 258 (EG)

nows has to be pulvoured mechanically and steacted with unhydrous hydrogenchloride to form Truchlorosilane. With the help of catalyst the steaction takes place at a nominal temp. of 30°C. The steaction leads products like sicly and chlorides of impurities, ht this point purification process occurs. It has to be done by fractional distillation as the products trichlorosilane and unwanted chlorides are liquids at soom temp. Purified 5itcl3 is subjected to chemical vapour deposition then it is reduced with hydrogen results electronic grade silicon and recovery of Hal.

courstal growth (sucation of ignots)

contol ogstem cioccuitorg.

Eas is a polycogstalline stoucture. Cz process is used to convert polycogstalline silicon into single cogstal silicon agnot. The moderial is then heated to a temperature 1500°C ie, slightly inexcess of silicon melting point 1420°C. A small single constal soot of silicon called seed constal is then dipped into the silicon melt. The conduction of heat the seed coystal will produce a reduction in temp of the melted incontact with seed constal to slightly below si melting point. The si will forceze opto the end of seed conjetal and end of seed crystal is slowly palled up of the melt it will pullup solidified mass of SE that will be a constalloguaphy continution of seed caystal. Both seed crystal and crucible are rotated but in opposite discettons dusting the constal pulling

paocess invadea to pavoduce constalline ign ingots

temperature and pulling rate are correctly chosen. The diameter of ingot is controlled by pulling rate and diameter of obout 100-150mm (4-6 inches). The ingot length will generally be the order of 3m. The crystal pulling is done in an inext gas atmosphere usually Ax Ox He and sometimes vaccum is eased. This is done to prevent, oxidation.

The furnace consist of crucible, crucible suppositional mechanism, Heating element and power supply and a chamber. The crucible material should be chemically unreactive with molten se, also the material should have high melting point, thermal stability and hardness. The material used for crucible is silicon nitrice and fused silica. Graphite is ased as crucible supposit as is it has high temperature proporties.

The caystal pulling mechanism consists of scaled shaft on chain, notational mechanism and

of dignowth process-pull rate and crystal riotation.

The pulling mechanism must have minimum violation and grant procession.

Relationship bla pull state and conjetal diameter

$$L \frac{dm}{dt} + K_L \frac{dT}{dx} P_1 = K_S \frac{dT}{dx_2} P_2$$

$$\frac{d\sigma}{dx} \rightarrow \text{Temp genadient of } \infty$$

$$\frac{d\tau}{dx_2}$$

$\rightarrow$  Temp, gradient of  $x_2$

to square soot of caystal sadius. This is based on I order heat balance equ. which represents dominant heat flux changes during forcess, or is the constant temp surface which is isotherm just inside liquid. Dusting forcezing paocess which occurs bla these 2 points heat sicleased to allow the malted 97 toursform to solid state. This heat must be semoved form forcezing interface. It is a poismonly porocess of beat townsher upto the solid ingot when the caoss sectional areas preparational egu. O is neglected and equi will be i dm, where de de amount of forcezing per unit time

DEDONIE DESCRIPTION OF POST OF POST AND AND THE POST OF POST O

The control of the police of the part of t Amount of facezing - auto A -> Caoss s

Vp -> Pulling state ... A-> Cross sectional area

on many mensity of St communitions with proportions

(2) => L Vp AN = KS dT A2 South seed my temble of strong strong

madeinsum pulling state, Vp = Ks dt A2 = Ks dt dx2

Travelling of section of travel

Floatzone paocess is suited for small water production with low oxygen impusity. Here a poly caystalline Eas and is fused with single conjetal seed of desired direction and oxientation. This is taken in an inext gas farmace and melted along the length of the god by an taravelling RF coil. The St will : faceze onto the end of caystal seed and as the seed constal is slowly pulled out of the melt, it will pullap a solidified mass of si that will be a caystallogaphic continution of seed egystal. The movement of RF coil starts from the fused siegion containing seed and towards up as shown in sigure. When the coll moves up the segion below solidifies

with same caystalline oaientation as that of the seed caystal. The surrace is silled with an ineutgas like that to acclude gaseous impusity and odd desisted concents. Of dopand this since no caucible is needed it can be used to paraduce oxygen face si austers.

Disadvantage. - The difficulty is to extend this technique for large water since the process produces large no. of dislocations and hence it is used for small scale applications requiring low oxygen content waters.

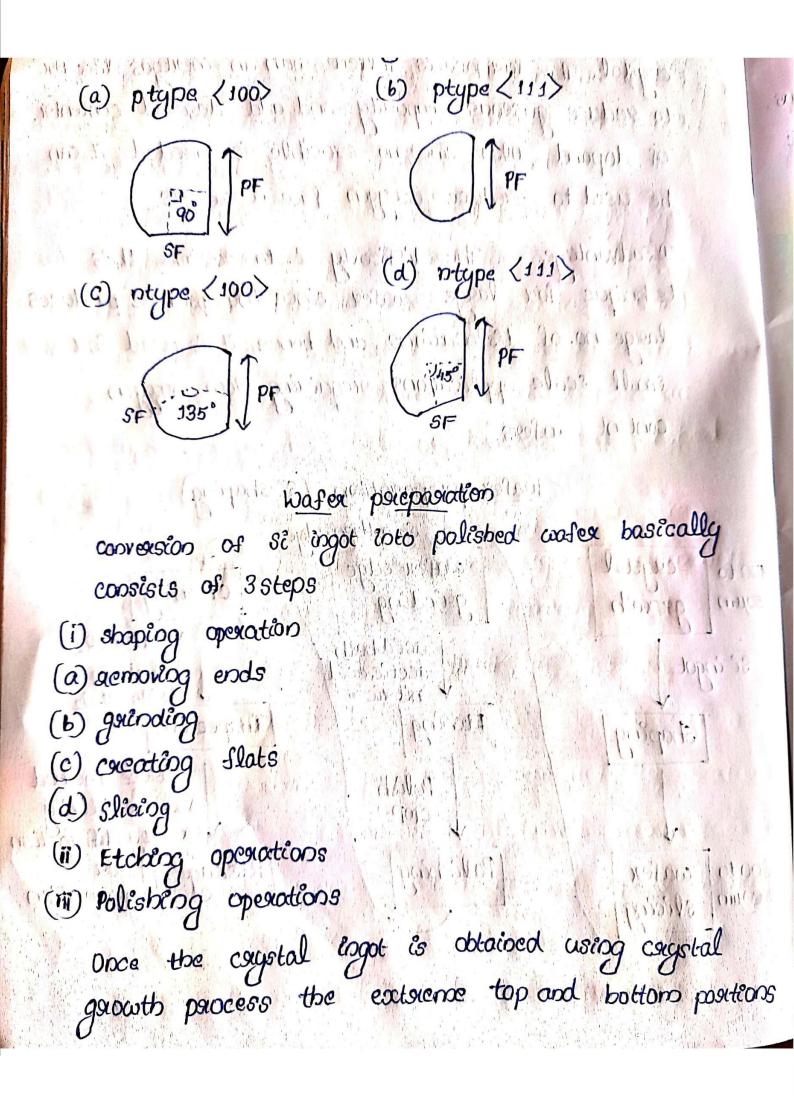

tipped saws. And the ingot sweface is goowed to peroduce a constant and exact diameter with it is usually 100,155 on 150mm. Besone processing further ingots are checked for resistivity and orientation using 4 point perobe technique (for presistivity) and or stay differentiation at both ends. After this I am more flats are ground along the length of ingot. There are 2 types of flat -> primary flat - This is a ground related to specific egystal dispection. This act as a visitual suctexence to the oxientation of water and also as a mechanical locatox in the automated processing equipment.

> secondary flat - This is used for identification of worker, depart type and oxientation. After making the flats the individual confers are sliced proper securious thickness. Inner diameter slicing is most commonly used technique. As a final shaping step edge containing when a suddius is ground on the sings of the worker.

etched trustuling any dumage and contaminated stegions.

This is usually done in acid both with a minutuse of Hel, with a cid and acetic acid.

Polishing-the swefaces are polished firstly by a sough abbrasive polish and followed by a chemical mechanical polishing procedure (cop).

In crop since Sio, particles suspended in a acqueous sodium byderoccide solution is used. Wasers one typically, single sided on double sided polished.

Decidation parties to the conversion of 81 works to 87 and 81 and 82 and 83 and 83 and 84 and

Prompose of growing oxide on 82

- · To serve as a mask agazort impliant on diffusion of depoint into si

- · To perovide surface passintion.

- To italize one device form another (dialectric italizan as appared to junction isolation.

- . To act as a component to 1908 staucture.

- · To pervide electrical isolation of mattlevel metalization caystals.

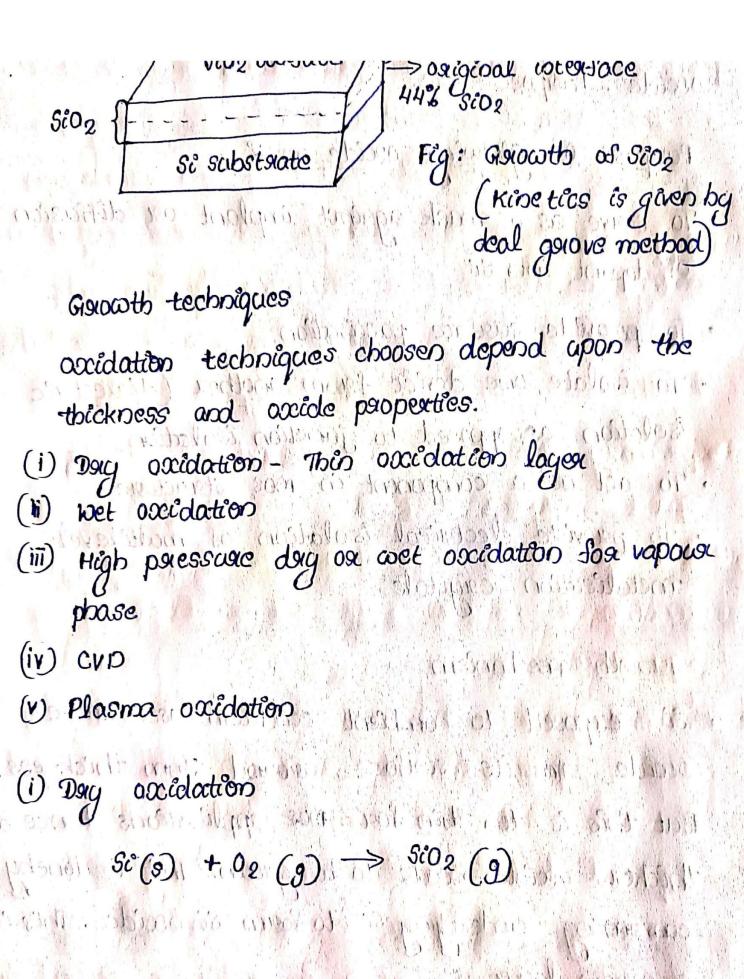

# Garath mechanism

Si exposed to ambient condition as a native outde on its surface, around 3nm thickness. But this is too thin for 1905 applications hence a thickness outde needs to be grown. This is doneby coordinate and underlying si to form si overde. This is a grown layer.

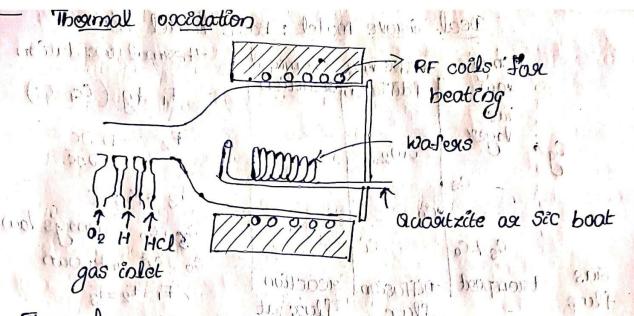

Thermal oxidation is a way to produce oxide layer on the surface of si water. This process torces an axialising agent to diffuse into water at high temp and react with it. Thermal oxidation usually personned at a temp. blace 800 and 1200°C resulting a high temp.

Daide layer. It may either use water or molecular oxigen as the axidant.

The oxidising ambient may also contain several % of HCl. The Chlosine sumoves melted ions that may occur in oxide layer.

Kinchics of Sion growth

| Gras diffusion        | 1) 1     | Gas          |             |

|-----------------------|----------|--------------|-------------|

| Solid state diffusion | 1        | 8802         | gainal y -  |

| Sloz fosimation       | 1. 11/30 | Se-substrate | Property 3. |

| 1. 1. h. | Henry 5            | of diffusion   | chemical<br>xeaction               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (cc,-cs)    |

|----------|--------------------|----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Cg       | layer Co           | St02           | · 92, [] ]                         | THE PARTY - I THE STATE OF THE | 7 200       |

| ic Lauk  | $C_{S} \neq C_{0}$ |                |                                    | Co, Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Henry's how |

| flax     | teconsposit        | Tlax<br>-      | seaction  <br>flux at<br>A cotesti | $F_1 = F_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -E          |

| By m     | FI                 | F <sub>2</sub> | F3                                 | n de podru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | JoH ich     |

Deal gave model used top predicting oxide theckness for thempoly oxides larger than about 300 Å.

(18-0.1 mm) be it describes kinetics of si oxidation.

This model is generally valid for temps bla, 700 and 1300 c. The refuse 402 concentration in figure are,

Cg - Conc. of 02 in gas stream for from the water Cg - Conc. of 02 in the gas at the surface of si oxide interface.

Co - Conc. of 03 in the oxide at outer surface of water.

Ci - Conc. of oxidising species at inner surface of confer.

Ci - Conc. of oxidising species at inner surface

Oxidising species are occygen, transported from

bulk of gas phase to the gas interface with such Fi (gas townsposit slux). Townsposited across excisting oxide towards si with slax F2 (distusion slux). React at the St. Sto2 interface with fluor Fg (seaction flux at interface.

· Fox steady state condition Fi.F2=F3.

· By gas law, PV. NKT ox P. N = C\*= C If flax F, can be linearly approximated by assuming that slave of oxidant som gas phase to gas oxide intenface is propositional to the difference of oxidant concentration cg and cg. Fing (cg-cs); cg is directly propositional to Pg and Co is directly pappositional to Company points principles

$$\frac{P_g}{kT} = \frac{N}{V} = C_g \qquad (Bg Gas law)$$

$$\frac{P_g}{kT} = C_g \qquad (D_g Gas law)$$

$$F_{i}$$

.  $hg$   $\begin{cases} \frac{P_{g}}{g} - P_{s} \\ \overline{kT_{ij}} \overline{kT_{ij}} \end{cases}$   $\begin{cases} \frac{P_{g}}{kT_{ij}} - \frac{P_{s}}{kT_{ij}} \\ \overline{kT_{ij}} \overline{kT_{ij}} \end{cases}$

where K is the Boltzman constant By-> Partial pressure of 02 is gas in home . .... gas adjacent to oxide scuface

Hensig's law states that equilibrican concentration of

peropositional to partice positioner swaroanding gas.

C\* & Pg on C\* + HPg H-> constant Illoulge, Co = HPS office at interloca. Sab in equ. of flux F,  $F_{I} = \frac{hg}{W_{I}} \left( \frac{c^{*} - c_{0}}{c^{*}} \right)$  | h  $\rightarrow$  Gas phase mass teransfer coefficient HKT Sharmon proposed in solid.  $F_2 \propto \frac{c_0 - c_0}{c_0 - c_0}$  where  $f_1 = c_0 + c_0$  and  $f_2 = c_0 + c_0$ in exchange in proposed in the to the factor of  $F_2 = \mathcal{D}\left(\frac{C_6 - C_6^2}{9ma} \cdot 2\right)$ If the flux F2 is a clated to the movement of the oxidising species with the oxidising lager ox diffusion of the oxidising species. Fick's law of diffusion Distusion is propositional to concentration gradient conc. gradient is defined as the statio of diffusion En concentration to thickness of oxide. Cooc. gaadient of Co-Ci on or of the Fo d Co-Ce some single with the contract of th

D → Diffusion coefficient ocide thickness

Flux F3 is related to reaction of Si with oxidising species. Fz & Ci

F3-Koco

$K_S \rightarrow Rate$  constant of SE occidation

under steady state condition Fir F2=F3

Equating F3 and F1 Equating F2 and F3

$K_{S}C_{i}^{\circ} = \underline{hg} \left( C^{*} - C_{o} \right) \qquad \mathcal{D}\left( \underline{C_{o} - C_{c}^{\circ}} \right) = K_{S}C_{i}^{\circ}$ Esta HKT in

Ksci = bgc\* - bgcb

HKT HKT

80 = 1 + K500 6x

DCo - CiD = Ks Croc

$\mathfrak{D}C_0 = C_i \left( K_S \mathfrak{X} + D \right)$

Cc = DCo

$$K_SC_i^2 = \frac{K_S C_0}{\left(1 + \frac{K_S x}{D}\right)}$$

$\frac{\partial^{2} h(c^{+}c_{0})}{\partial t} = \frac{\partial^{2} h(c_{0})}{\partial t} = \frac{\partial^{2} h(c_{0$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{D} \right)$$

$$k_{S} + h \left( \frac{1 + k_{S} x}{$$

when diffusibility of and Co=ct. Here the oxidation process purely controlled by diffusion. Here oxidation nate depends on supply of axidant to the surface

is no difference blu the 1+ ks conc. of oxidising species from outer and inner surface. Here the oxidation rate depends upon chemical reportion rate constant (ks) so it is called reaction controlled oxidation.

To calculate state of oxide growth are define not as the not of oxide molecule in a unit volume of oxide layer. Growth state characteristics can be obtained by dividing the flux at interface by the not of molecules of oxidents per unit volume of  $\frac{dx}{dt} = \frac{F_3}{N_1}$

$$F_{3} = \left| \frac{1}{8} \tilde{c}_{c}^{2} \right| + \left| \frac{1}{1} \tilde{c}_{c}^{2} \right| + \left| \frac{1$$

$$\frac{dx}{dt} = \frac{kscs}{N_{J}}$$

No

$$\frac{dx}{dt} = K_SC_0^2 = K_SC_0$$

$$\frac{K_SC_0^2 + 1}{D} = \frac{K_SC_0^2 + 1}{D} = \frac{K_SC_0^2 + 1}{D} = \frac{1 + K_SC_0^2}{D}$$

$$\frac{K_SC_0^2 + 1}{D} = \frac{1 + K_SC_0^2}{D} = \frac{1 + K_SC_0^2}{D}$$

$$N_1 \frac{dx}{dt} = \frac{K_S C^*}{1 + K_S + K_S x}$$

$$\int \left[ 1 + \frac{k_0}{h} + \frac{k_0 \infty}{D} \right] d\infty = \int \frac{k_s c^*}{N_i} dt$$

$$x + \frac{K_S x}{b} + \frac{K_S x^2}{2D} = \frac{K_S C^* x + P}{N_I}$$

$$\frac{2}{2} + \frac{1}{2} \times \frac{1}$$

$$P = \left(1 + \frac{Ks}{b}\right) \chi_i^s + \frac{Ks \alpha_i^s 2}{2D}$$

$$\begin{array}{c} x + \frac{k_s x}{b} + \frac{k_s x^2}{2D} & \frac{k_s c_k * x + \sqrt{1 + \frac{k_s}{b}}}{2D} & \frac{\kappa_s c_k * x + \sqrt{1 + \frac{k_s}{b}}}{2D} \end{array}$$

$$0x^{2} + x\frac{2D}{Ks} + \frac{x}{b} 2D = c \times \frac{2Dt}{N_{I}} + \left[1 + \frac{Ks}{b}\right] \frac{x^{2}}{2D} + x_{i}^{2}$$

$$x^{2} + x\left[\left(1 + \frac{\kappa_{s}}{b}\right) \frac{2D}{\kappa_{s}}\right] = \left[2 \frac{c^{*}D}{N_{1}}\right]^{*} + x_{c}^{2} + \left[\left(1 + \frac{\kappa_{s}}{b}\right) \frac{2D}{\kappa_{s}}\right] x_{c}^{2}$$

Let

$$A = \left(\frac{1 + Kg}{b}\right) \frac{2D}{Kg}$$

$$13 + 2c*D$$

$$\Rightarrow x^2 + \theta x - 8t + x_i^2 + \theta x_i^2$$

$$= B \left[ + \left( \frac{x^2 + Ax^2}{B} \right) \right]$$

$$x^{2} + \theta x - B(t+3) = 0$$

$$x^{2} + \theta x - B(t+3) = 0$$

$$x = -\theta \pm \sqrt{\theta^{2} - (4x - B(t+3))} = -\theta \pm \sqrt{\theta^{2} + 4B(t+3)} = 0$$

$$\theta = \theta = 0$$

$$\theta =$$

$$AS t \rightarrow 0$$

,  $x = \frac{B}{A}(t+\overline{b})$ , linear  $A \rightarrow 0$ ,  $A = \frac{B}{A}(t+\overline{b})$ , linear  $A \rightarrow 0$ , parabolic

migral with the length couper , say to white

(ati) t

follows a linear state of growth when took oxidation follows a possobolic store of goodth.

Relationship blw oxide govowth and oxide thickness x 6+ 4x -8 (++2) = 0

$$x^{\ell} + Ax = B(t+\overline{b}) = 0$$

$x^{\ell} + Ax = B(t+\overline{b})$

diff. w. st. to to on both sides

$$2x \frac{dx}{dt} + \frac{dx}{dt} = B \frac{dt}{dt} + 0$$

[  $t = constant$ ]

$$(2x+1)\frac{dx}{dt} = B$$

dr => occide goiowth side ((1))

$\infty \rightarrow \infty$  occide thickness

doc slows dows withour increase in oc.

Impublity segulegation

Impusities both intensional and unintentional are intenduced into si ingot intentional doponts one mixed into melt olcowing enystal growth. While

different solubility in solid and melt. And equille. Seguagation, coefficient k. can be defined as noted of equilic conc. of impurity in solid to that in liquid.

$K_0 = \frac{C_S}{C_L}$  (Conc. of impusity in solid)

9 Cz paocess

In si ingot which should contain 10<sup>16</sup> Boxon atoms/cm³ is to be govern by Cz technique. What conc. of Boson atoms should be in melt to give the stequised conc. in ingot If the initial land of si in the caucible is coky. How many governs of Boson (atomic weight = 10.8) should be added. The density of molten si is 253g/cm³. Given sequegation constant ko = 0.8.

f) Given,

no. of bosion atoms =  $10^{16}$  atoms/cm<sup>3</sup>

malten Silican = 60 kgko = 0.8Atomic weight = 10.8Density of Si =  $2.53g/\text{cm}^3$ Ko =  $\frac{C_s}{C_L}$   $C_L = \frac{C_s}{K_0} = \frac{10^{16}}{L} = 1.25 \times 10^{16} \text{ cm}^3$

```

Dorostly of 38

GOX 103 29. -115 x 103 cm3

Conc. of bosion atoms in the melt - C, * melt volume

1.20×1016×2.3.715×103

2.96 x 1020 Boston atoms

1 Avagadoro

No. of genons of Boxon. 2.96 x 10.8

10.89

Theamal a oxidation

2) A 1000 A Séo2 layer grown in long o2 at 1000°C followed

by 0.5 µm thick axide in wet oxidation at some temp.

Determine total time of oscidation.

Given, a 0.1 m

B. 0.12 µm2 / box

B/A = 0.07 un/box

x^2 + Ax = B(t+7)

Activas Somme

(0.1 x106)2 + 0.1 x106

ty = 1.8-1 has

```

$$8 (8/A) J.27 J.27 J.27 O.J13h948 O.J27 O.J13h948 O.J27 O.J$$

Mathematical analysis of diffusion inpuder to fully characterise diffusion we need to determine following posameteus,

- (1) How for clopant otomo go inside the semiconductor atoms 1 (2) Doplog perofile

- (3) where the junction is present

- (4) conc. of improvity at sanface.

- (5) Det emine there we need to perform mathematical apolyeis

Constant source diffusion 11110 (x Impusity concentration at the surface is is maintained at a constant level thoroughout the distusion cycle. Bourdony conditions cone, c(0,t)=cs, c(x,t)=0,0(00,0)=0

Solving Fick's law.  $C(x,t) \cdot c_s \exp\left(\frac{x}{2\sqrt{Dt}}\right), t>0$ exist -> complementary exercises function of -> distance in cm oc -> distance in cm t -> Time fox diffusion in seconds. D -> Diffasivity eafc (x). 1- eaf(x) ex f(x) = 2 / ex day somoto tought is to cold (1 To obtain total amount of impurity, Q = (a, i) dx  $\int c(x,t) dx = \int c_s \operatorname{ext}_c\left(\frac{x}{2\sqrt{Dt}}\right) dx$ Let  $\left(\frac{x}{2\sqrt{DE}}\right)^{\frac{1}{2}}$  is hosti for proof some cloc = dz. 2 \Dt  $Q_{7}$ ,  $\int_{C_{8}}^{\infty} e^{y} dz$  (x)  $2\sqrt{Dt} dz$ Co 2/Dt (cofc(x) dx

Depth of diffusion, c(x,t) -  $c_s$  ease  $\frac{x}{2\sqrt{Dt}}$  $C_{\mathcal{B}} = C_{\mathcal{S}}^{(n)} exsc \left( \frac{x_{\mathcal{S}}^{(n)}}{2\sqrt{Dt}} \right) \left( \frac{x_{\mathcal{S}}^{(n)}}{2\sqrt{Dt}}$ Let CB be the ant of impusity in semiconductor before caseign out the diffusion also called background diffusion. The depth of diffusion is equal, to the backgaround cope of parity. Cost = C8 fox depth of diffusion c(x,t).  $c_s$  enfo  $\frac{x}{2\sqrt{pt}}$  $\frac{C_B}{C_S} = eg.fc\left(\frac{x_j^{\circ}}{2\sqrt{Dt}}\right)$

In the fabrication of manalithic ics constant source diffusion is commonly used for isolation and emitter diffusion because it maintains high scurface conc. by a continuous intenduction of abpant.

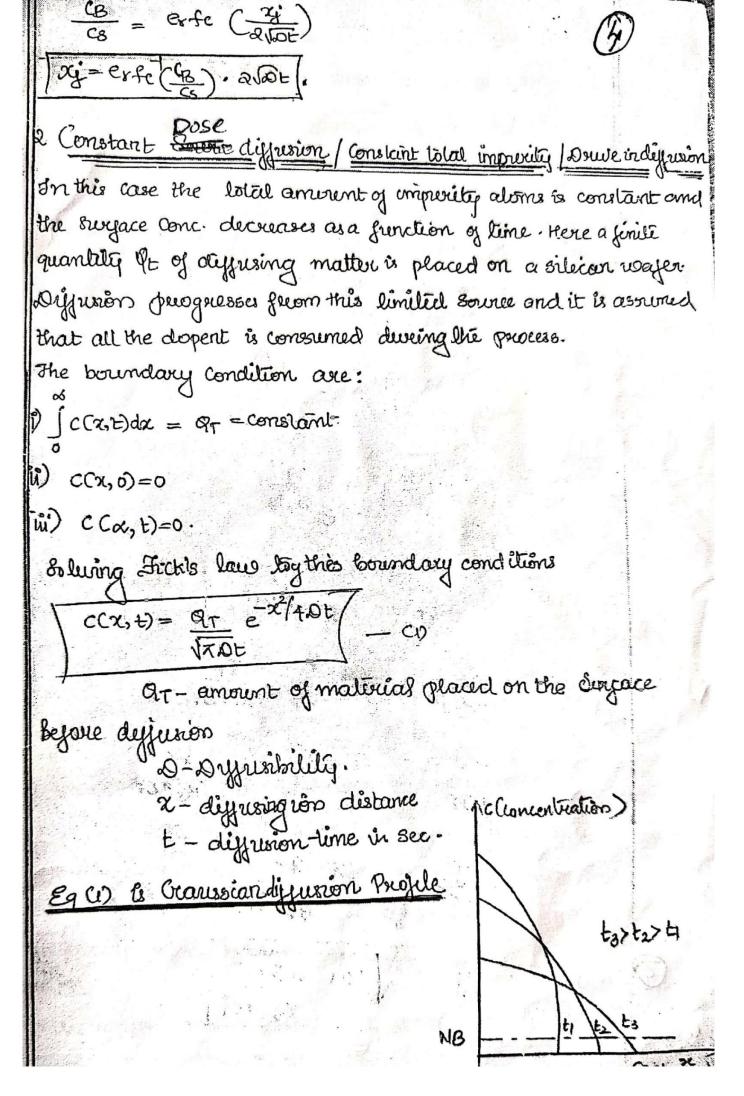

Limited source diffusion / const dose diffusion / prive in D

Here it predetermined ant of impurity is introduced into the crystal, the diffusion takes place in 2 steps

and deposited on se wasen during a sposit-teme.

(ii) Derève en step-Impusity source es tweed off and anot of impusities already deposited during = step alie allowed to diffuse into the se water. with these type of dissusion the depth of the penetsiation of impusitles dusting paie deposition step is assurand to be megligible as composed to the final are depth after completing the drive cycle. Gaussian

(1)  $\int_{C}^{\infty} (x,t) dx = Q_{T} \quad \text{constabt} \quad \text{conc.} \quad \uparrow$ (2)  $C(\infty,0) = 0$

(3) c(4,6) = 0

Solving Fick's Jaw,  $c(x,t) = \frac{8\pi}{\sqrt{\pi}Dt}$

distaibution

In this case total and of imposity atoms is constant and southice conc. decreases as a function of time. A finite quantity of diffusing matter is placed on se wofer diffusion paragaresses faion this limited source and 18th is assumed that all dopont is consumed during the parocess.

at most of material placed on surface before n -> Distasion coefficient ac -> " distance t -> " time and the por Develor Sasiface concentration It can be calculated by substituting o in equ.  $\sqrt{\pi Dt}$  =  $\frac{e^{-\alpha c^2/4Dt}}{\sin \omega t}$  surface conc. decreases Cs QT Topico doth Idention depth

It is the point in the isomiconductor were impurity Janction depth conc. is equal to background doping conc. i.e., at  $c = C_B$  and  $x = x_0^2$ CB - 1 TIDE ( CHIM) CHI SOLON IN e 2 /ADE CB TODE of stop let is done desire of the stops it to tilling in dop in the language of p a constant some

$\frac{C_{B}\sqrt{\pi Dt}}{Q_{T}} = \frac{1}{e^{\infty j^{2}/4Dt}}$   $e^{\infty j^{2}/4Dt} = \frac{Q_{T}}{C_{B}\sqrt{\pi Dt}}$ Taking natural log on both sides,  $\frac{2j^{2}}{4Dt} = \ln \frac{Q_{T}}{C_{B}\sqrt{\pi Dt}}$   $2j^{2} = 4Dt \ln \frac{Q_{T}}{C_{B}\sqrt{\pi Dt}}$   $2j^{2} = 4Dt \ln \frac{Q_{T}}{C_{B}\sqrt{\pi Dt}}$

Diffusion systems

Impusities are diffused form their compound source. The method of impusity delivery to the water is determined by nature of impusity source. 2 step diffusion is widely used technique. Type of impusity diffusion whether complitmentary evans in distribution on Gaussian distribution is determined by the choice of operating condition.

2 step diffusion consists of pac-deposition step and drive in step. In the Josephsen step a constant source

diffusion is cassifed out for short unity to the temp. 100°C. In later step impurity supply is shut off and existing dopont is allowed to diffuse into the body of seniconductor at a temp. 120°C in an exidising atmosphere. Oxide layer which forms on the surface of answer during this step prevents further impurities from entering, already deposited impurity preside is a for of diffusion conditions, a temp, time and diffusion coefficients.

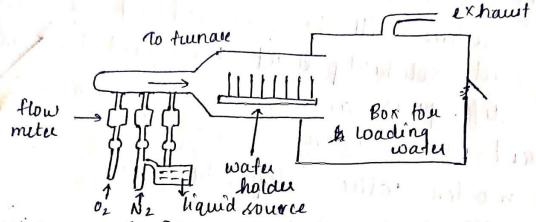

#### Diffasion famace

From the various type of diffusion process a sessistance heated tube favinace is a discally used. Tube favinace has a long hollow opening into which a quantz tube about 100-150mm in diameter is placed. Temp. of favinace is kept at 100°C, temp. within favinace can be controlled by 3 individually controlled adjascent resistance clements. So where to be processed one stacked up vertically into slots in a quantz boot, and invent into the farinace tube.

D = 10 16 m2/sec at 1150°C Solid solutility 5x1026 atomos/m3 Diffusion of ptype impusity, boston is an exclusive choice as an accepted impunity in st. It has a moderate D, which is convenient son paccirely controlled diffusion. Surface conc. can be widely varied due to ets solid solability. Quantz Si waters boat 800c foge pooding In loading holder

B2H6 02 N2 (psicincipal gas)

(Gioseocis 90-99%

Sociace)

$\begin{array}{l} \text{Si} + 0_2 \rightarrow \text{SiO}_2 \\ 2B_2H_6 + 36_2 \rightarrow B_2O_3 + 6H_2 \end{array}$

Boxon diffusion using diboxone source is a gaseous source of bosion. This can be disectly interoduced into diffusion funce. A no. of other goser and metered into funnace. Principal gas flow in the favorace will be No which acts as a gelatively inext gas, and is used as a cassilest gas to be a délatant don other mone ocactive gases. Na canaled gas well generally makeup 90-99% of total gas flow. A small and of of and very small omt of gaseous source of Boson well makeup nest of gas flow. The following reactions will be occurring semultaneously at the scorface of se wasers. This process is a chemical vapous deposition (CVD) of a glassy loyex on si swiface, which is a mixture of Si gloss and Boson gloss is called Boson Silica glass (BSG). BSG glassy layer és a viscous liquid at a diffusion temp. Bosson conc. In BSG is s si swiface will be saturated with Boxon at solid solubility limit throughout time of diffusion process as long as BSG siemains priesented. This is a coastant source diffusion. It is often called deposition diffusion

## Mathematical Amagies of Difficion In order to fully characterise diffusion we need to deturning the following parameters o how for the dopent atoms mais go inside the semicondudo along. I don't e doping perofile O where the frenction & person O Conc. of imprivilty at the Buyace. To determine these powermeless we need to & porform mathematical analysis. 1. Constant surjace concloysusion from un limited source

Here the impurity conc at the someonductor surjace

& maintained at a constant level through out diffrence cycle. The boundary conditions are C(0, t) = C8. CCs is the surjace concentration) C(oc, t) = 0 Clone. of comparaty at x=0. gnom surject) c (x, 0) = 0 (conc. of improvity before difficients a convictoret). solving Fick's law the boundary condition.  $c(x,t) = G ex Fc \left(\frac{x}{a\sqrt{D}t}\right) t > 0$ Exfe - complimenting ever function x- distance in con. or fir) = The 2 - 20 yrusionvily constant t - time for deffusion in sec. enfect) = (- exten) Sertech) de = The plot shows that wisespective of the duration during which diffusion is laveried out all the 3 comes starts at G. ie snowfa Cone is always Constant To oftain Total Amount of Imprisity To calculate the total consunt of improviley which has been introcluced into the semiconductor during dyfrinon we calculate the area under the aviace

$$QT = \int_{0}^{\infty} e(x,t) dx$$

$$= \int_{0}^{\infty} c_{\delta} \exp \left(-\frac{x}{2\sqrt{10}t}\right) dx$$

$$\text{Let } \frac{x}{2} = x.$$

$$\frac{dx}{a\sqrt{a}t} = dz$$

$$dz = a\sqrt{at}$$

$$dz = a\sqrt{at}$$

$$dz = a\sqrt{at}$$

$$dz = \sqrt{at}$$

$$dz = \sqrt{at}$$

## n Depth of Diffusion

Let Co be the amount of impurity in the semiconduct before coverying out diffusion this is also called as back-ground concentrations.

The depth of diffusion on function occurs when the Conc of impossing due to adjustion is equal to the back of acound conc. Let this depth be  $X_1$  then at  $x=x_1$ .  $C=C_B$

# Surface Concentration

of can be calculated by substituting x=00 in eqcit

# Trenction Depth

It is live point in Beneconductor whole the impush is equal to the backguound dopping conce.

$$c(x_j;t) = \frac{9\tau}{\sqrt{\pi o}t} e^{-x_j^2/40t} = c_0$$

$$\left( \frac{CB\sqrt{\pi D}F}{QT} \right) = \frac{-3e^{2}}{640E}$$

$$CB \sqrt{\pi \omega t} = \frac{1}{2J^{2}/40T}$$

$$\frac{e^{3J^{2}}}{440T} = \frac{CB \sqrt{\pi \omega T}}{440T} = \frac{OT}{OT}$$

$$\frac{e^{3J^{2}}}{440T} = \frac{CB \sqrt{\pi \omega T}}{OT} = \frac{OT}{OT}$$

$$\frac{e^{2g^{2}}}{4.0T} = \frac{CB\sqrt{X0T}}{9\pi} \frac{4007}{CB\sqrt{720T}}$$

mix fue of silica & Boson glass, is called

The Bsbi , is a vision liquid at diff. tempuatruses.

The Boson conc. in Bs in is such that the si surface will be saturated we boson at a solid solubility limit throughout the time of diff. process as long as Bs in remains present. This is a const. Source Diff.

et is offen called deposition ditf.

Diffusion of ptype impurity

This diff. step is reterred as predeposition step in which the dopant atom deposit into the surface segions of hi water

The borossilica glass is pretenable because it protect the si atoms trom pitting on evaporating and act as getter for unclensable impulities in the si.

The predeposition step is tollowed by a second deff process in which the external dopand some. (BSU) is removed such that no additional (BSU) is removed such that no additional dopanets enter the si. During this diff. process, dopanets enter the si. During this diff. process, the dopants are already in the si, more further and are their redustribuled.

The Jn. depth Tees and at the same time, the sentace cone. decreases. This type of diff. is called driving on limited source diff. ( yoursian distribution)

Boson Ditt using Boso Boson tou Bromide Souce:

This is a liquid source of Boson in this case, a controlled flow of Laceier gas is bubbled through Brenon tribsomide soln. which with Oxygen again produces been Boson trioxide (Boso vilica Glass) at the

Solution of the washes as put the above eqn.  $4BBr_2 + 3D_2 \longrightarrow B_2D_3 + 2Br_2$   $S_1^2 + D_2 \longrightarrow S_1^2$  (gray)

Dithusion of N-type Impulity:

For Phosphorow diff. such compounds as phosphine LPH3) and Phosphorow Oxythloride (1043) can be used in this case of diff. using pous, the suarchons occurring at the si water sufferer will be

nan

4 POU3 - 2 P2 D5 + 6 Cl2 (Phosp.glass)

This will result in the product of grassy layer on the si water that is a mixture of Phosp. glax & si glass called Phosphososilica glass (PSU) which is a viscous liquid at ditt. temp.

The mobility of Patom in this glassy layer and this P cone is such that , the P cone at & surface will be maintained at solid solubility limit throughoud the time of diff. process.

The rust of the proocess tor p diffusion is similar to Boson diff. i.e., affer prediposition step, diving during deposit diffusion is caused out.

Other common N-type dopants are Antimony and Amenic These doparts have low diff conet. Therebow, they are wetred materials too earlier diff. stages such as Not build layers. Antimony is sometimes preferred because ît's les toxic but assenic has a higher solid solubility limit and can provide bigger surtaire concentration of dopants.

From the second that is not and the

in the display of me trust tours. and.

The Medical Control of the State of the Stat

ment of the manner of the second of the second

. M. Marie in American

### Puopenties of Diffusion:

- Deolid solubility & dopart 1, SC 1

- 2) Diffusion timp.

- s) Pithusion time.

- 4) soutail cleanliness and detlets in & cystal.

- per unit volume can be added tou a specific diffusion, that means, humber of atoms per unit vol. must be less than solid solubility limit.

- entire area.

- 3) BH. Time: Include a diff hime of diff. Locof. D have similar effect on in depth. For gaussian distre, the net conce will decrease also to Impurity compensation and can approach o with increase in diff. Hime.

Fou constant source ditt, net impulity the diffused side of pn gn. shows a steady state inclease with time.

4) The si suitair must be prevented against contaniminant deuing ditt. which may interfere with unitarnity of diff. profile.

The crystal defects such as dislocation may to produce localize impulity conc. This results in the degradation of in chaia.

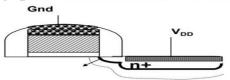

MODULE: 2.

15591: Method of isolation ext component Fabrication:

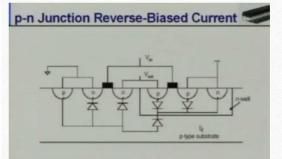

Yaris ditt. platu. x axis diff. plates. luon Implantation: light u and electe - First Mutical watu. source.

white it is a world in the terms of the

lon Implantation. Impuelty profile.

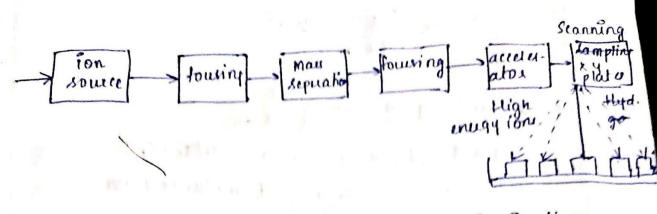

Ion implantation s/m consists of:

i) con source

ii) man separaton

iii) acceleration hube

iv) scanning s/m.

contains derived implant species like Assane, Phosphane and Boson tu Husuide (BF, feed

The field gas is exposed to à high energy is which is produced by heating a filament using elettie weent.

These high energy is strike the tred gas & break the moleulu to form individual atoms.

Mars syruator;

Lons extracted from source contain deff. ion species

tuavel at a relatively & speed into mass lep. chamber. chamber consists of an anaylzed magnet shaped at go. Mg. filld of analyzu magnet lause the ion species to be detlected into an acc. If the mg. field strength o B, lon charge is Q, then the ion moves in a circle of radiu given by  $r = \frac{1}{B} \frac{\int dVm}{a}$

Vm is the source volt- into mass of ion. The mg. field B can be adjusted such that only the desired ion will pass through the stit and others will be rejected. print was a said

Acceleration hube: To achieve additional ion accelliation, the Pons which come out of m.s are accelerated in an E inside the the acc- wlumn.

Inclasing the acc. voltage will incuase the ion implantation on jn. depth into the water.

Scanning slm:

Electrostatic scanning deflects ion beam across a stationary water by applying specific controlled volt to a set of ny deflection plana.

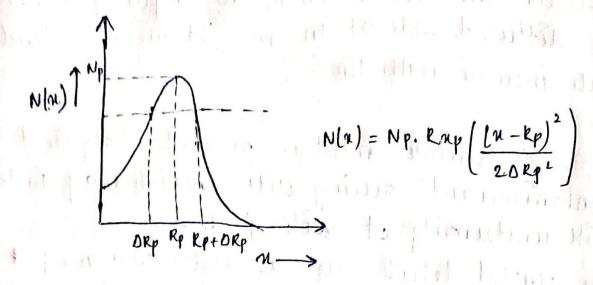

ion implandation puotile: (gragn deawn before)

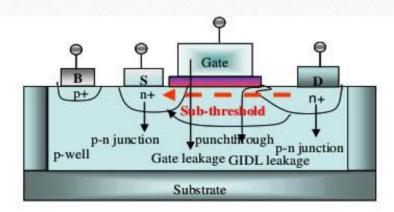

#### Range Theory:

lon stopping: As each implanted ion enters the target, it undergous a series of collision with target atome until 9+ finally come to rest at some depth.

This depth is called projected range expressed in

Purojuted range depending on impurity used and the implantation energy.

There are 2 basic ion stopping mechanism by which an energetic ion are brought to rest 1) Nucleus stopping .... In his lasting

2) E shipping. I hat militie win com in home and

Nucleus Atopping: The tre ion scatters as it encounters trely charged nucleus. The nucleus stopping & elastic so the energy Lost by incoming ion is transferred to the target atom. Thus, it distorate the target nuille teem their orginal state. is jet istnown granodati to a contract of the second of

. 100 implantation perofile in a gaussian distribution.

· Implantation of ions expressed as a to of dist x toom

$N(n) = Np. exp(-(x-kp)^2)$ the surface

where Np is the peak cone of implanted ions. when n=kp.

N(n) = N(Rp) = Np.

$Np = \frac{0}{\sqrt{2} \pi Rp} = \frac{0.40}{0 Rp}$

Q's the implantation tous dose given by

Q = 1 / I dt, where A = area of implantation. I = tondr Implantation

beam current

DRP à straggle deviation in projected mange.

LSS Theory of lon Implantation:

Electron stopping: It is caused by the intuaction of ion with a cloud of is surrounding the tauget atoms. Eleuteonie stopping & gêven by:

$$Se = \left(\frac{dE}{dn}\right)e = KJE$$

# Nucleus stopping on = (dE)

Total stopping power = N(se+Sn) N=no. of implanted ions

$$S_T = N \neq \left(\frac{dE}{du}\right)_t + \left(\frac{dE}{du}\right)_n$$

Implantation dosage Q: It is the no. of implanted ions per unit surface area.

$$Q = \frac{1}{A} \int \frac{I}{9} dt$$

Annealing:

After the ions have been implanted; they are I They are lodged principally in intestitial position, in the Si cuptal structure and surface region into which the ion implantation has taken place will be heavily damaged by the impact of high energy ions. The disc-array disaway of si atoms in the surface region is often open to the extend that this surface region is no longer ceystalline in structure but

region back to well-ordered crystalline state and to allow implanted ions to go into the substitutional sides in the crystalline struct. The water must be subjected to annealing process.

The annealing process usually involve heating of waters at a temp. of 1000°c. tou about so mins.

Most commonly used annealing techniques are laser beam L i beam annealing.

In such annealing techniques only the studace sugion of the water is heated and succeystallized.